- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

Hi all,

My customer is using i.MX8M Nano UL Solo.

They want to change core clock to 1.4 GHz which is the highest speed for that processor.

They find a function "clock_init" in arch/arm/mach-imx/imx8m/clock_imx8mm.c.

it initializes core clock as below,

/* Configure ARM at 1.2GHz */

clock_set_target_val(ARM_A53_CLK_ROOT, CLK_ROOT_ON |

CLK_ROOT_SOURCE_SEL(2));

intpll_configure(ANATOP_ARM_PLL, MHZ(1200));

/* Bypass CCM A53 ROOT, Switch to ARM PLL -> MUX-> CPU */

clock_set_target_val(CORE_SEL_CFG, CLK_ROOT_SOURCE_SEL(1));Customer has below questions about these codes.

- what does "CORE_SEL_CFG" means? It is defined as 49, but I cannot find it in reference manual.

- function "intpll_configure" accepts 600MHz, 750MHz, 800MHz, 1000MHz, 1200MHz and 2000MHz.

When it is set to 2000MHz is core frequency over clock state? or capped to maximum frequency? - code "clock_set_target_val(ARM_A53_CLK_ROOT, CLK_ROOT_ON | CLK_ROOT_SOURCE_SEL(2));" seems to set "SYSTEM_PLL2_DIV2" as ARM_A53_CLK_ROOT. should it set to CLK_ROOT_SOURCE_SEL(2) ?

Thanks.

已解决! 转到解答。

refer to your code, do your customer want to change the cpu frequency in uboot ?I think maybe you misunderstand them, they should want to change the cpu frequency in kernel, right? pls double confirm this, if yes, they can refer to the chapter 2.5.3 CPU Frequency Scaling (CPUFREQ) of enclosed file

Thank you for the information.

I found the word "CORE_SEL_CFG" in IMX8MP reference manual, which have different source select from it in IMX8MM.

anyway, I will try to SYSTEM_PLL1_CLK in u-boot.

Please replay another questions.

these 2 questions I asked at the first post,

> 2. function "intpll_configure" accepts 600MHz, 750MHz, 800MHz, 1000MHz, 1200MHz and 2000MHz.

When it is set to 2000MHz is core frequency over clock state? or capped to maximum frequency?

> 3. code "clock_set_target_val(ARM_A53_CLK_ROOT, CLK_ROOT_ON | CLK_ROOT_SOURCE_SEL(2));" seems to set "SYSTEM_PLL2_DIV2" as ARM_A53_CLK_ROOT. should it set to CLK_ROOT_SOURCE_SEL(2) ?

additionally, CORE_SEL_CFG has different source select in IMX8MM and IMX8MP. What source select does CORE_SEL_CFG have in IMX8MN UL?

as I mentioned before, CORE_SEL_CFG is listed in the imx8mm, but imx8mn RM remove it, this should be the different from the imx8mm, the file you refer to is for imx8mm, maybe you can set according to the imx8mm, I'm not sure if this is available again for imx8mn

Thank you for answer.

So, how to supply a maximum speed clock, 1.4GHz to A53 on i.MX8M Nano UL?

Which Clock source to set, and how to route it?

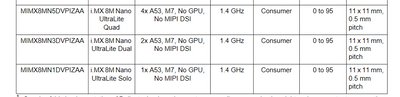

DS says the processor's speed grade is 1.4GHz (as below), but RM does not say how to do it.

Is the CPU speed grade in DS wrong?