- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- How To Troublshoot UBoot SPL Not Loading

How To Troublshoot UBoot SPL Not Loading

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

How To Troublshoot UBoot SPL Not Loading

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

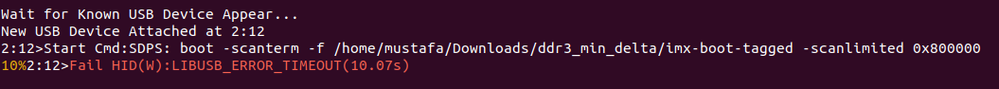

We have a custom board based on the imx8mn-ddr3l-evk SOM, except it uses DDR4 instead of DDR3L. We have been able to create a custom BSP (modify uboot & imxboot) and successfully boot Linux based on past imx BSPs, with the latest version being on LF5.15.71_2.2.0 (uboot v2022.04). However, we just attempted to update our BSP to LF6.1.55_2.2.0 (uboot v2023.04), and we are getting the error below when trying to load the generated yocto image using UUU. The full output is attached.

We believe the SPL is not loading, and we don't think it is a DDR init issue. We do not get any output on the UART console, and the PMIC rails voltages are not being configured, which is one of the SPL functions that is called before the DDR init function. We put multiple console messages at different stages within spl.c and are getting nothing. We know the board is okay cause we are able to boot our latest image compiled based on LF5.15.71_2.2.0.

The board files (<machine>.conf, <machine>_defconf, <machine>.dts, spl.c, etc.) in this BSP are very similar to the old working BSP with few changes introduced to match updates introduced to imx8mn_evk board files. We tried multiple configurations and still got nothing out. We basically have the following questions:

- Are all machines included in the imx yocto release (ex: imx8mn_evk.conf, imx8mn_ddr3l_evk.conf, and imx8mn_ddr4_evk.conf) have been tested to boot Linux?

- Can a JTAG connection with a JLink Flash debugger offer us more useful information? Is there any documentation to follow? I see some for other debuggers (e.g., ARM DSTREAM), but I'm not sure if we can use segger JLink.

- How can we access BOOT ROM Log Events? AN12853 discusses the available info, but we're not sure how to access it if SPL is not loading. We thought JTAG, but imx8mnrm states that JTAG is not accessible during the initial ROM boot.

- Any ideas on how to troubleshoot this issue and move forward? We are running out of ideas.

Thank you.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @moose

Please refer new BSP to port board files(this is very important),some configurations maybe changed between Uboot2022 and Uboot2023. There are two reasons that may cause this issue:

(1)Some configurations about USB download in Uboot are nor correct and this cause SPL can't be loaded by USB.

(2)SPL configurations issue,please check your porting steps.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

@Zhiming_Liu, please answer questions 1-3. Copied here again for reference:

- Are all machines included in the imx yocto release (ex: imx8mn_evk.conf, imx8mn_ddr3l_evk.conf, and imx8mn_ddr4_evk.conf) have been tested to boot Linux?

- Can a JTAG connection with a JLink Flash debugger offer us more useful information? Is there any documentation to follow? I see some for other debuggers (e.g., ARM DSTREAM), but I'm not sure if we can use segger JLink.

- How can we access BOOT ROM Log Events? AN12853 discusses the available info, but we're not sure how to access it if SPL is not loading. We thought JTAG, but imx8mnrm states that JTAG is not accessible during the initial ROM boot.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Q1: Yes, these conf files has been tested on corresponding board.

Q2 :You can use Jlink

Q3:Jlink is for load SPL to ocram ,not for debugging ROM events, i don't think you need get ROM events.You load SPL to ocram, then ROM will run from that address and see serial log from SPL.