- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- 8MMINID4 Reference Design + eMMC boot issue

8MMINID4 Reference Design + eMMC boot issue

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Supporter,

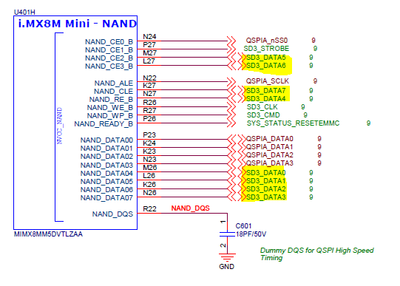

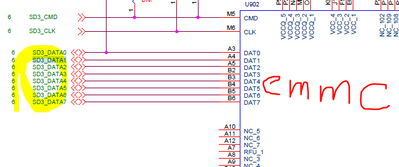

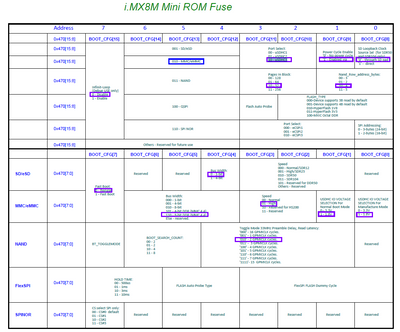

We follow 8MMINID4 to design a new HW and replace NAND to eMMC as below.

We can update image successfully by using UUU tool. Please check UUU log and uuu.auto for command list.

After reboot, it will hang up at u-boot and complain "MMC Device 1 not found".

Can you help to check and advise?

boot up log:

U-Boot SPL 2019.04-lf-5.4.y_v2019.04+g48508669 (Dec 02 2020 - 02:47:35 +0000)

power_pca9450_init

DDRINFO: start DRAM init

Training FAILED

DDRINFO:ddrphy calibration done

DDRINFO: ddrmix config done

Normal Boot

Trying to boot from MMC2

MMC Device 1 not found

spl: could not find mmc device 1. error: -19

SPL: failed to boot from all boot devices

In U-boot prompt, we can found eMMC device at port2.

log:

u-boot=>

u-boot=> mmc list

FSL_SDHC: 2

u-boot=> mmc dev 1

MMC Device 1 not found

no mmc device at slot 1

u-boot=> mmc dev 2

switch to partitions #0, OK

mmc2(part 0) is current device

u-boot=>

Regards,

Kenny

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

In the software the uSDHC3 clock is not initialized in default. We must let CONFIG_SYS_FSL_USDHC_NUM=2 to run the uSDHC3 clock initialization code. How to add you can refer to the thread by my colleague.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Which uSDHC are you using for emmc? uSDHC1?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Any update?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

In the software the uSDHC3 clock is not initialized in default. We must let CONFIG_SYS_FSL_USDHC_NUM=2 to run the uSDHC3 clock initialization code. How to add you can refer to the thread by my colleague.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks a lot. It can enter kernel now.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Good news it works now.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告