- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Processors

- :

- i.MX Processors Knowledge Base

- :

- Using the i.MX8M Audio System

Using the i.MX8M Audio System

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

Using the i.MX8M Audio System

Using the i.MX8M Audio System

The NXP i.MX 8M provides industry leading audio, voice and video processing for applications that scale from consumer home audio to industrial building automation and mobile computers.

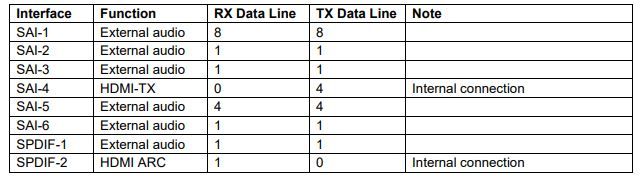

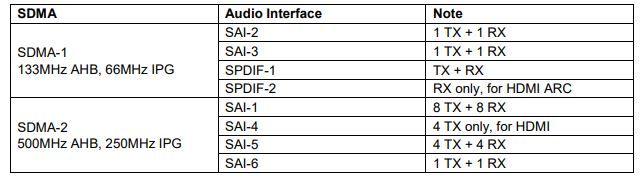

The i.MX 8M Quad supports multiple audio interfaces as listed below:

Besides the general audio input/output function, the audio interfaces will supports following features:

- SAI-1 supports up to 16-channels TX (8 lanes) and 16-channels RX (8 lanes) at 384KHz/32-bit.

- SAI-5 supports up to 8-channels TX (4 lanes) and 8-channels RX (4 lanes) at 384KHz/32-bit.

- SAI-2/3/6 supports up to 2-channels TX (1 lanes) and 2-channels RX (1 lanes) at 384KHz/32-bit.

- SAI-2/3/6 support up to 2-channels TX (1 lane) and 2-channels RX (1 lane) at 384KHz/32-bit.

- SAI-1 supports glue-less switching between PCM & DSD operation for popular audio DACs

- SPDIF-1/2 supports raw capture mode that can save all the incoming bits into audio buffer

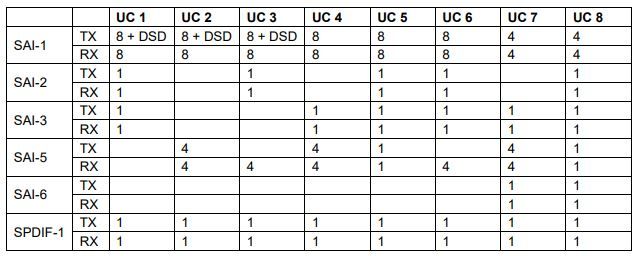

The SAI-1/2/3/5/6 and SPDIF-1 share GPIO pads on the chip through IOMUX. Common use cases supported by the audio interfaces are listed in the table below (many other configurations are possible). The number is the data lanes supported.

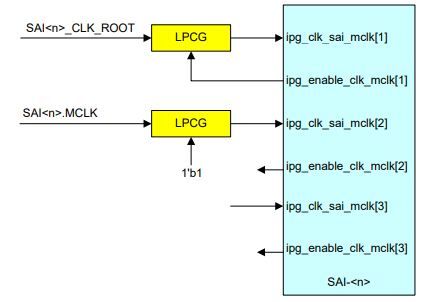

For the MCLK pin on each SAI module, it can be configured as either input or output. When configured as output, the SAI_CLK_ROOT from CCM will be routed to the pad output. When configured as input, the external input to the pad will be routed to SAI.MCLK, which can be used as master clock for SAI. Below is the diagram showing the both input/output options, by using SAI1 as the example.

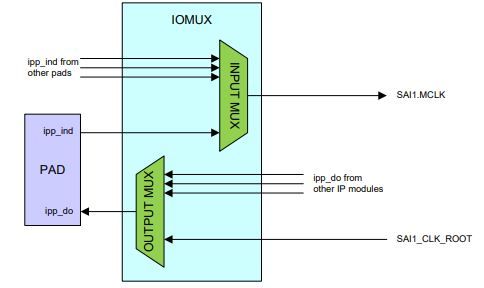

Each SAI module supports up to 3 master clock inputs. The TX and RX sub-module inside each SAI can independently select one of the clock inputs as its master clock. This allows TX and RX of one SAI to run from different clock source. The master clock inputs have following options:

- SAI.MCLK[1] can be selected from SAI_CLK_ROOT from CCM or SAI.MCLK from IOMUX. This is the most straight-forward clock routing in which SAI only use its own clock source from CCM or IO pad.

- SAI.MCLK[2] can be selected from following clock sources:

Any of the SAI_CLK_ROOT from CCM;

Any of the SAI.MCLK from IOMUX;

Other clock sources from SPIDF;

- SAI.MCLK[3] has exact same clock source options as SAI.MCLK[2]. This allows both TX and RX can have access to all the options without any dependency between each other.

The clock options for master clock on SAI are shown in the diagram blow, by using SAI-1 as an example.

The options on MCLK[1] is also available on MCLK[2] and MCLK[3]. The reason to keep this options is to provide the similar SAI clock structure as i.MX6/i.MX7 processors. The configuration of the MUX for master clock are controlled by IOMUXC_GPR registers. They should be configured before SAI clock is enabled to avoid glitches on the clock.

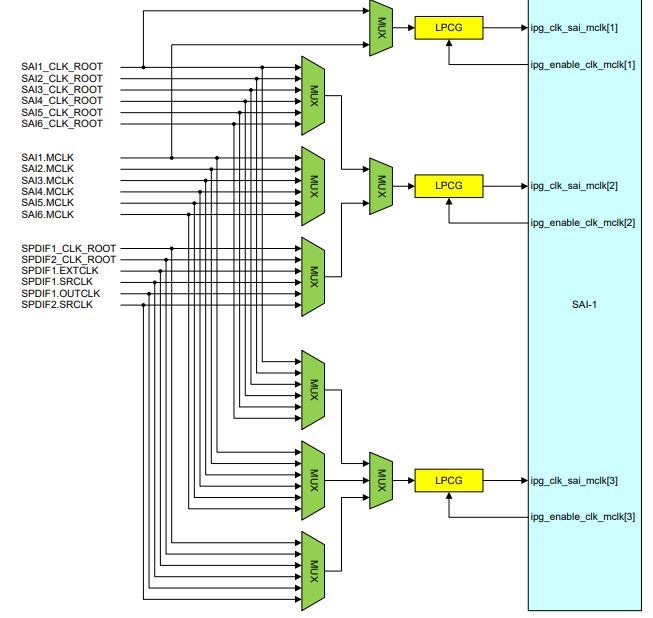

Note: Because those MUX on clocks are missed during the design, the actual implementation in the silicon is simplified as shown in the following diagram.

All the SAI and SPDIF instances have SDMA support. In order to meet the audio data rate, two SDMA modules are used.

Because the SAI-2/3 and SPDIF-1/2 do not require high data throughput, they are assigned to SDMA-1, shared with other peripherals such as UART/SPI. SAI-1/4/5/6 need to support high sample rate & multichannel audio, they are assigned to SDMA-2, which is a dedicated SDMA engine for audio. The SDMA-2 frequency is increased to 500/250 instead of 133/66 to make sure it has enough throughput.

In order to allow SW tracking the progress of audio DMA, the TX_SYNC and RX_SYNC of SAI modules are routed to GPT as the external clock input. Since there are totally 6 SAI modules, these signals will be MUXed when connection to GPT.

- GPT-4/5/6 external clock input can be selected from the TX_SYNC or RX_SYNC of any 6 SAI modules;

- The MUX select is controlled by IOMUXC_GPR register;

- The MUX select register for GPT-4/5/6 are fully independent of each other.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Thank you Xiaocong Fu