- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- Home

- :

- SafeAssureコミュニティ

- :

- Forum

- :

- The list of registers for SM4.RGSTCHCK, SM4.AIPS_SWCHECK

The list of registers for SM4.RGSTCHCK, SM4.AIPS_SWCHECK

オプション

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

The list of registers for SM4.RGSTCHCK, SM4.AIPS_SWCHECK

03-27-2024

08:33 AM

212件の閲覧回数

HeebeomPark

Contributor II

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Can you specify the list of the registers between SM4.RGSTCHCK and SM4.AIPS_SWCHECK?

We opened S32K3xx_REG_PROT_detail.xlsx however it looks it is somehow duplicated with the following registers, which was informed by NXP.

| Register | Category |

| Crossbar Integrity Checker (HSE_B & AES_ACCEL AXBS_Lite) ERM_1 | SR |

| Software Watchdog 3 Trigger Multiplexing Control Body Cross Triggering Unit | SR |

| eMIOS_0 eMIOS_1 eMIOS_2 | SR-AD |

| Logic Control Unit 0 Logic Control Unit 1 | SR-AD |

| System crossbar switch Crossbar Integrity Checker (System AXBS / AXBS Lite) Crossbar Integrity Checker (Peripheral AXBS-Lite) | SR |

| eDMA control & status (MP_CSR; MP_ES; MP_HRS) eDMA transfer control descriptor 0 eDMA transfer control descriptor 1 eDMA transfer control descriptor 2 eDMA transfer control descriptor 3 eDMA transfer control descriptor 4 eDMA transfer control descriptor 5 eDMA transfer control descriptor 6 eDMA transfer control descriptor 7 eDMA transfer control descriptor 8 eDMA transfer control descriptor 9 eDMA transfer control descriptor 10 eDMA transfer control descriptor 11 | SR |

| RAM controller 0 | SR |

| Flash controller Flash controller alternate | SR |

| Software Watchdog 0 | SR |

| System Timer Module 0 XRDC | SR |

| Interrupt Monitor DMA Channel Multiplexer 0 DMA Channel Multiplexer 1 Real-time clock Reset Generation Module | SR |

| 32 kHz Slow Internal RC Oscillator | SR |

| 32 kHz Slow External Crystal Oscillator | SR |

| 48 MHz Fast Internal RC Oscillator | SR |

| 8-40 MHz Fast External Crystal Oscillator Clock Generation Module Mode Entry Module | SR |

| Frequency Modulated Phase-Locked Loop Frequency Modulated Phase-Locked Loop 2 | SR |

| Power management controller | SR |

| Flash memory Flash memory alternate | SR |

| Programmable Interrupt Timer 2 Programmable Interrupt Timer 3 | SR |

| FCCU (+FOSU) MU_0_MUB JDC (JTAG Data Communication) Configuration GPR | SR |

| Self-Test Control Unit | SR |

1 返信

03-27-2024

02:42 PM

206件の閲覧回数

NXP Employee

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

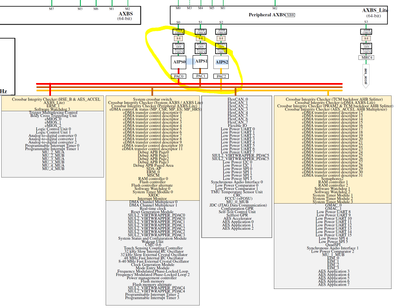

It is really the same registers. The AIPS allow you to gain access to the peripheral registers with the use of three AIPS busses for the S32K388. See diagram below. Essentially for the AIPS check you would just need to check the value of registers that would excercise all three AIPS busses to verify the AIPS. For the Safety register check you would need to select safety relevant, for your application, registers and verify that the values what you would expect.

Regards,

John