- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- SafeAssure Community

- :

- Forum

- :

- Scheck swt fail

Scheck swt fail

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Scheck swt fail

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Teams

Customer's application based on saf version 1.0.0 and Rtd 2.0.1. Customer fix Scheck scheck swt bug manually according to the latest saf version. In sCheck_Swt_CounterTestRun , found that when set TO to 0x20 can pass test and then set TO to 0x10 can not pass test. but out of test loop, after disable swt in scheck. IR in swt is set and interrupt pending in core. and then after scheck, customer reconfigure swt, swt is dysfunction that the action of swt is not consistent with configuration. But this issue could not be reproduced by simple demo code.

customer wants to know:

- Ask which scenario will cause the test to fail.

- Customer wants to know the root cause of scheck swt fail.

Best Regards

Junjie

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The issue was tracked down to hardware of SWT. New errata is being reviewed at the moment. Once the errata is published SAF sCheck team will implement necessary workaround for future SAF releases.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

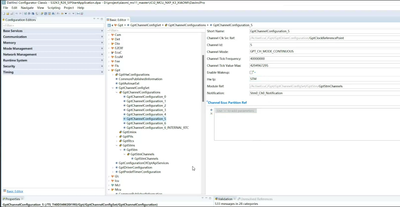

We check with customer that the STM0 selected for scheck and 40MHZ as below

Let's add more details about this case.

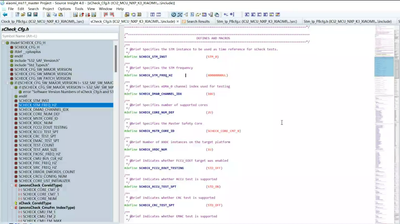

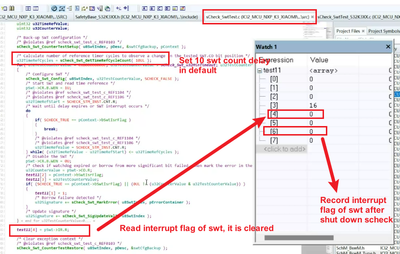

1. when keep 10(actually 17 count ) swt count wait time out, scheck test pass ,but customer reconfigure swt after shutdown scheck test, swt work in abnormal. actually in this swt count wait time out, Test should not pass when set TO to 0x10.right? so why we set this count to 10?

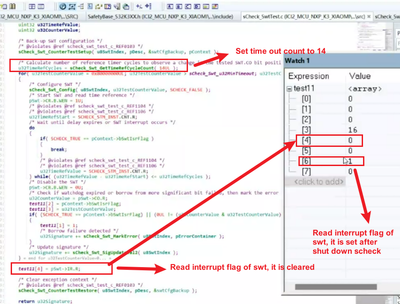

2. when modify swt count wait time out to 14(actually 21 count )scheck test pass ,customer reconfigure swt after shutdown scheck test, swt work in normal , but interrupt flag of swt was cleared in the end of test but set after shut down scheck,

3. when modify swt count wait time out to 17(actually 24 count )scheck test fail,customer reconfigure swt after shutdown scheck test, swt work in normal , interrupt flag of swt was set in the end of test and also set after shut down scheck。

so there are 3 questions from customer:

1. when set swt count wait time out to 10. why reconfigure swt after shutdown scheck test, swt work in abnormal?

2. when set swt count wait time out to 14, why interrupt flag of swt was set after swt disable?

3. why we set wait time out to 10 in scheck swt?

Best Regards

Junjie

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @Junjie, here are answers for customer:

- This needs to be clarified with HW team. I am working on that.

- This configuration is probably caused by race condition between SWT counter and STM counter. The test disables SWT right at the time of interrupt flag getting set, but SWT to CPU ISR reporting is not finished in this time.

- SWT timeout of 10 SWT cycles is set as longest timeout value which should not cause ISR to trigger. It is also sufficient timeout (with buffer) in which counter of SWT should change its counter value.

Could you provide detailed clocking details?

- CORE_CLK = ?

- AIPS_SLOW_CLK = ?

- SIRC_CLK = 32 kHz

- STM_0 = 40 MHz

Thank you, Jonas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

CORE_CLK=160M,AIPS_SLOW_CLK=40M

we have also reproduced this issue by simple demo as mentioned in teams. prerequirement: A/B HSE framework installed, swt reconfiguration after shutdown scheck , then reset will be triggered right now (not based on swt configuration).

Best Regards

Junjie