- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

SM_048 Implementation

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

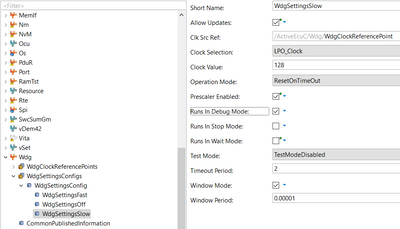

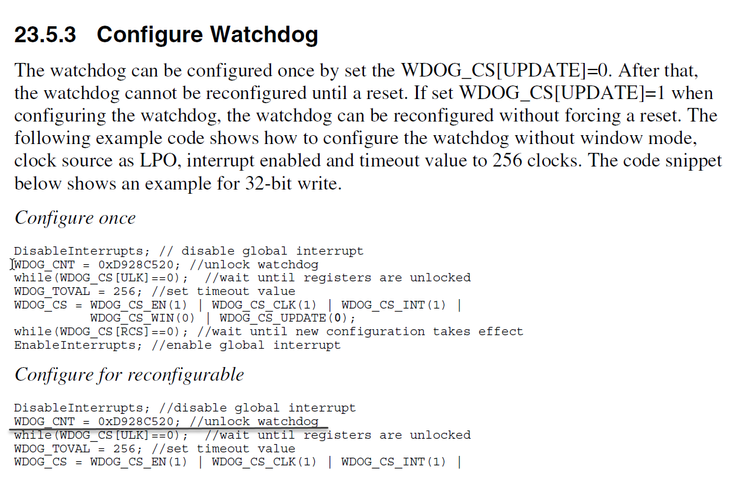

As per S32K1xx Series Safety Manual, Rev. 4, 09/2018 document for SM_048, DBG bit in the Watchdog Control and Status Register (CS) should be set to 1 and we are also using LPIT then LPIT_MCR[DBG_EN] = 1.

I am able to set the DBG bit to 1 by configuring the Wdg Run in debug mode parameter as shown below

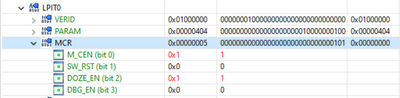

but when I try to set LPIT_MCR[DBG_EN] = 1, then my application is continuously resetting and LPIT_MCR[DBG_EN] bit is never getting set to 1.

Can you please let me know the correct procedure to set LPIT_MCR[DBG_EN] bit and also the implementation support to meet SM_048 requirement.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @manish_singh,

How do you configure the LPIT module?

Do you follow the steps in Table 48-4. Initializing the LPIT modul?

Anyway, when the MCU is in the active debug mode and the core is halted, the WDOG (with DBG = 1) cannot be refreshed, therefore the WDOG will reset the MCU.

Regarding SM_048, please read it in the context of the whole Section 5.6.2.1 Debug mode.

"The debugging facilities of the S32K1xx and S32K14xW pose a possible source of failures if they are activated during the operation of functional safety-relevant applications."

That is why we can have certain modules active even in this active debug mode, and in this case, the WDOG can reset the MCU.

Regards,

Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Daniel,

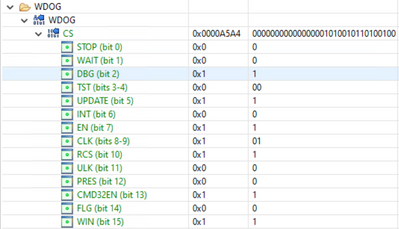

I am able to set LPIT_MCR[DBG_EN] bit to 1, but I am not able to set WDOG ->CS[DBG] = 1 from the code, these bits are only getting set only from the configuration, is there any way I can set it manually.

Source code I am using to set the WDOG ->CS[DBG] = 1

WDOG ->CS = 0x0000A5A4;

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @manish_singh,

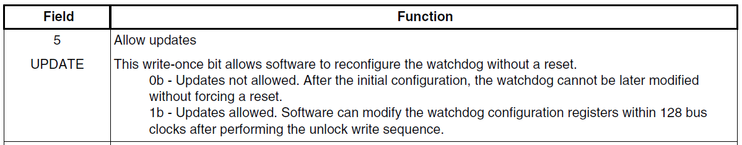

In the initial initialization of the WDOG, you need to set the UPDATE bit.

So, before you write the register, read it first, is UPDATE = 1?

Thanks,

BR, Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Yes, I have checked this condition but then also I was not able to set it.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I forgot to mention that the WDOG must be unlocked first.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I will try the suggested solution and update you.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

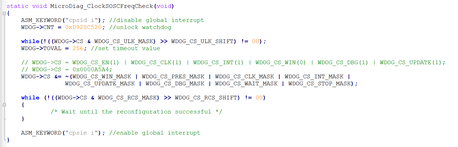

I have tried the suggested solution but I am not able to set WDOG ->CS[DBG] = 1, kindly find the below code for reference

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Manish,

Please double-check the code, it clears both DBG and UPDATE.

BR, Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I have updated the code but then also it was not getting set. Can we have a meeting to discuss on this ?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @manish_singh,

Please keep in mind that if the WDOG is enabled in the debug mode, and the core is halted by the debugger, the WDOG does not get refreshed, and the MCU is then reset.

Can you scope the reset_b signal while you are testing it?

Thank you,

BR, Daniel