- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: S32K344 Cs to Cs time issue in SPI

S32K344 Cs to Cs time issue in SPI

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S32K344 Cs to Cs time issue in SPI

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Team,

I am working with s32k344 series.

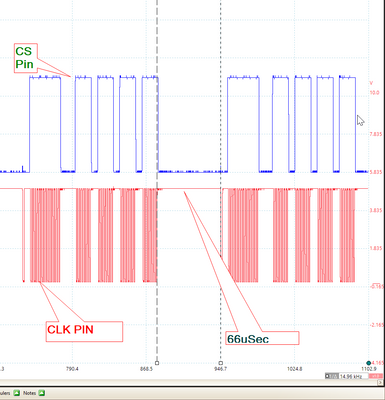

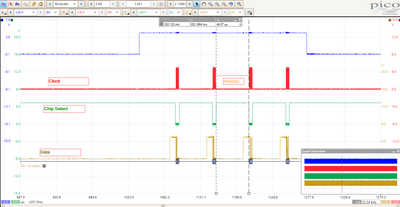

I am sending 4 bytes of two frame in 1ms task . getting 66 uSec delay between two frame.

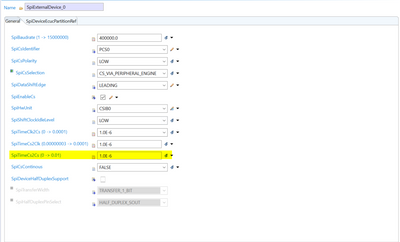

In tresos i have configure Cs to Cs time is 1uSec.

in code i have send two consecutive frame .

please suggest somewhere i am doing wrong setting.

Regards,

Shrikant Koli

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This is caused by the cpu overhead, you should see a shorter delay at a higher system clock frequency.

The driver needs some time to place the data into the TX FIFO.

If you sent all 8 bytes in one function call, the delay should not be there.

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello danielmartynek,

Thanks for your support.

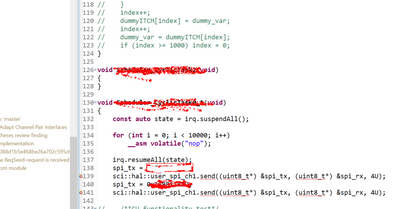

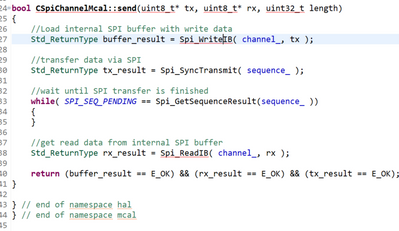

As you mention we tried this solution, instead of 8 we are sending 4 bytes in a one function call. before that we are sending 2 bytes in a one function call.

But whenever we called this function for next 4 bytes that time we get delay.

Additional information is that we are using internal buffer.

Regards,

Shrikant

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I not sure how exactly is the driver implemented.

But the LPSPI module keeps sending as long as there are data in the TX FIFO.

With the DMA, there should be no CPU overhead.

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

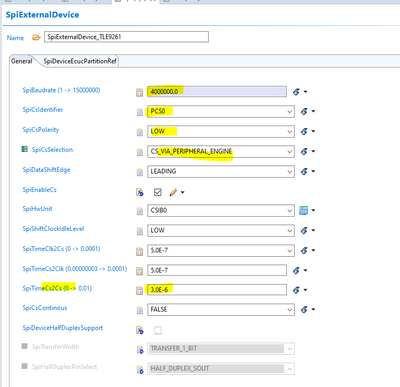

Please refer the our new configuration, this configuration we slightly modified.

Attached tresos configuration for your reference.

Chip select pin is active low and CS2CS time configures as 3uSec.

SPI reference clock set to be 30M.

look at the attached result .

In one frame we are transmitting the 2 bytes data.

Cs2Cs time is configured as a 3uSec but in image if you see that is approximate 44uSec.

We have check all the register setting that is correct as per configuration.

why the configuration made by the tresos does not have any impact on behavior.

Look at the below code : send function.

referring to the link : Re: How to Change SPI Data time interval With MCAL - NXP Community

same issue is happen with other users. NXP provided them workaround.

if possible provide this workaround to us. so we can try it out.

Regards,

Shrikant

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you send me the full configurations of your project via your case number 00546814

And how did you call your Send function in your project?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @cuongnguyenphu ,

I have attached here SPI related xdm files.

i have called this function cyclically into the 1 ms scheduler.

Meanwhile guide me how i can share the configuration through case number 00546814.

Regards,

Shrikant

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@shrikantkoli1995

You can access to https://support.nxp.com/ by your account, in Cases tab you can find a ticket number linked to this topic, then you can send to us some private information of your project that cannot share on this community