- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

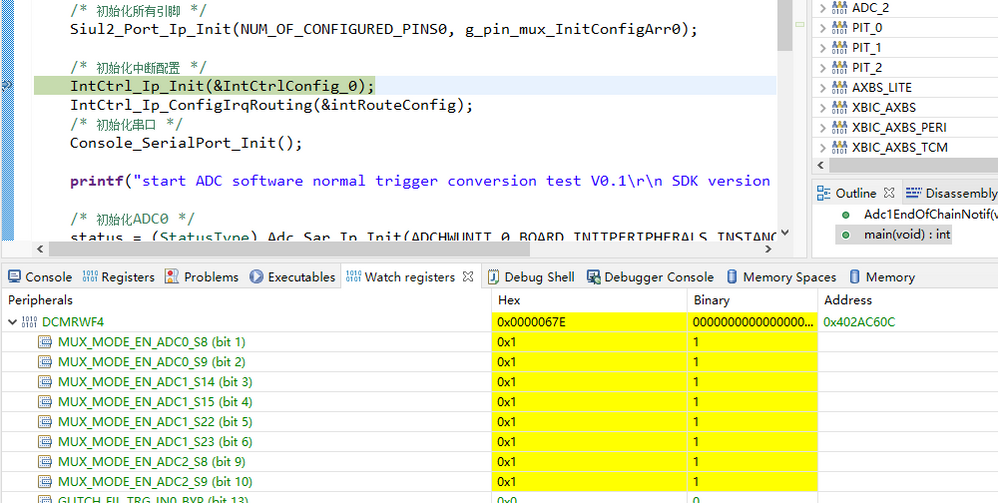

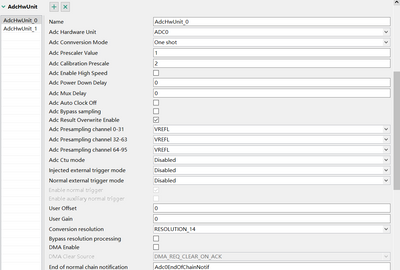

Using the ADC configured by S32K312, due to the large number of channels, some special pins are used. Some problems are encountered during use. The pin configuration does not take effect, and the ADC channel does not get correct data. I use the normal sampling mode. SW RTD2.0.0.

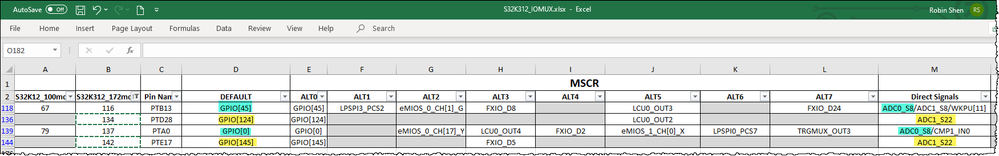

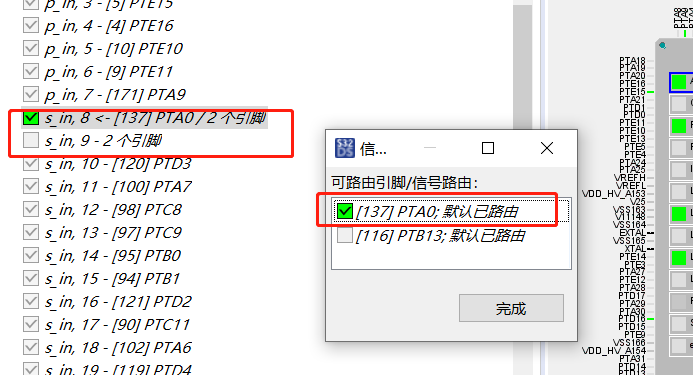

The first one: One ADC channel corresponds to multiple pins, such as s_in, 8. I checked PTA0 and used the PTA0 channel to collect the level, but the ADC sampling value of the 8-channel I read is incorrect. I still need to configure what?

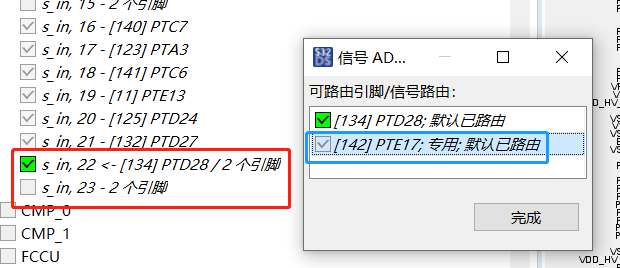

The second: like s_in, 23 s_in,22. I want to use the ADC to collect the PTD28 voltage, but my configuration does not take effect, and the voltage value of the PTD28 cannot be obtained. The system default is PTE17 and cannot be cancelled.

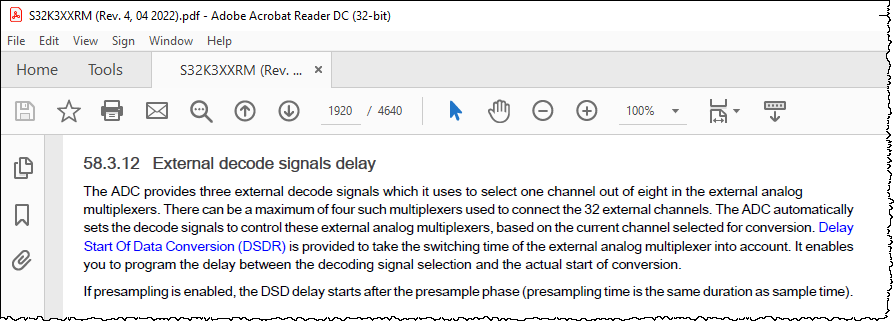

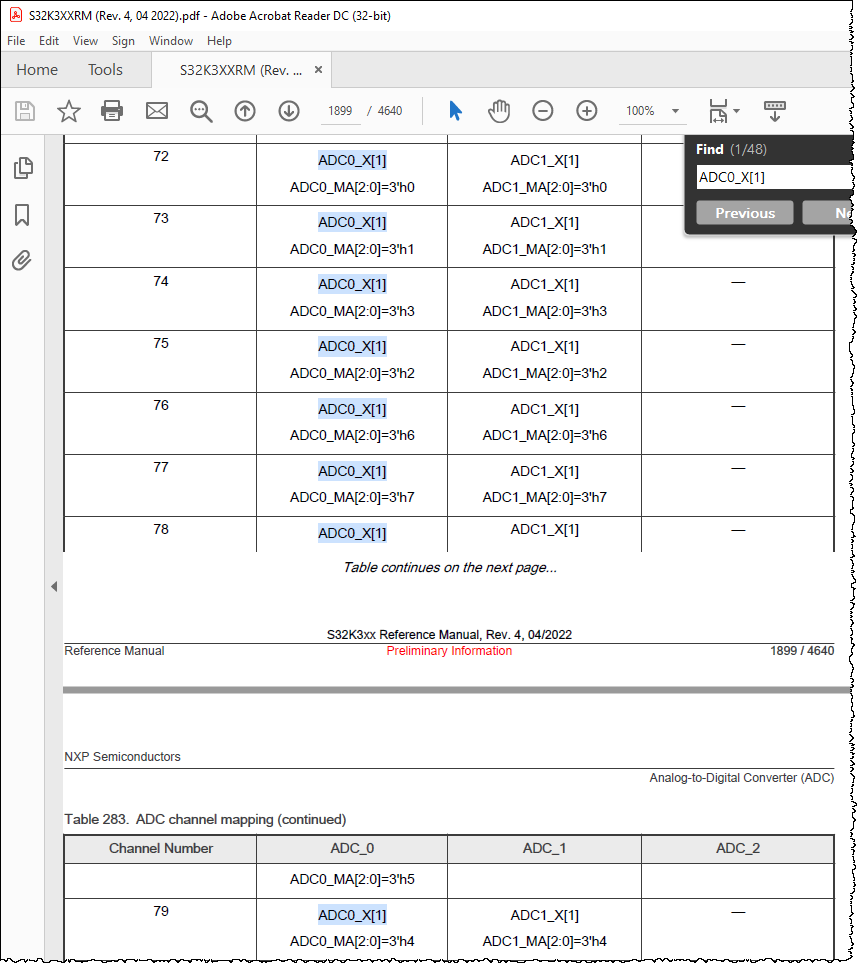

The third; is to configure the external input ADC, such as ADC0_X[1] I don't see much description in the RM manual, where should I go to get more information.

my configure

已解决! 转到解答。

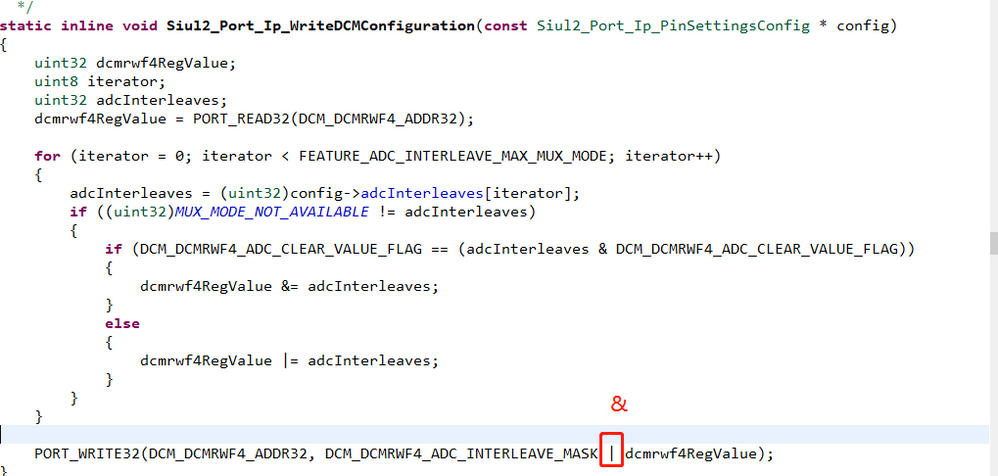

You are correct. Siul2_Port_Ip_Init() enables the ADC related bits in DCMRWF4 register by default. The RTD LLD version is SW32K3_RTD_4.4_2.0.0_DS_updatesite_D2204 and the running environment is S32 Design Studio IDE v3.4 Update 3.

It was reported several days ago. And the Proposed solution is what you did(Change the default "|" to "&" in Siul2_Port_Ip_WriteDCMConfiguration() API).

Sorry for the inconvenience we bring you!

Hi wuxianlong,

Q1\Q2: You can refer to the discussion in S32K344 ADC coversion result jump problem

Q3:Each ADC provides 3 external decode signals (MA) to be used to select 1 channel out of 8 in the external analog multiplexers.

The decoding signals for the selection of external ADC channels (ADC_X) are gray-encoded.

Best Regards,

Robin

Hi,@Robin_Shen

I wonder if the code needs to be modified.

You are correct. Siul2_Port_Ip_Init() enables the ADC related bits in DCMRWF4 register by default. The RTD LLD version is SW32K3_RTD_4.4_2.0.0_DS_updatesite_D2204 and the running environment is S32 Design Studio IDE v3.4 Update 3.

It was reported several days ago. And the Proposed solution is what you did(Change the default "|" to "&" in Siul2_Port_Ip_WriteDCMConfiguration() API).

Sorry for the inconvenience we bring you!

@Robin_Shenhi,

I verify the method of modifying the code, which seems feasible. Can you confirm it. If it is convenient, can you give me your contact information?

Hi,@Robin_Shen

Thank you for your help,

1、According to the description of the manual, the default value should be 0. No matter how configured the S8 channel is, it is 1, is it that I have not configured it successfully? I checked the code of RTD2.0.0 and found that the register change code is not running.

2、about the email

![DCMRWF4[MUX_MODE_EN_ADC1_S22][MUX_MODE_EN_ADC0_S8].png DCMRWF4[MUX_MODE_EN_ADC1_S22][MUX_MODE_EN_ADC0_S8].png](https://community.nxp.com/t5/image/serverpage/image-id/194856i01A6121971E25A39/image-size/large?v=v2&px=999)