- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

S32K148 - SAI TX overflows

Hello,

Is there any way to check if there are overflows on SAI0 TX FIFOs when DMA is feeding SAI?

The S32K148 Reference Manual specifies how to check if there was underrun, but I could not find similar interrupt for overflow. I would need this information as soon as overflow happens.

Thank you,

Jakub

Hi,

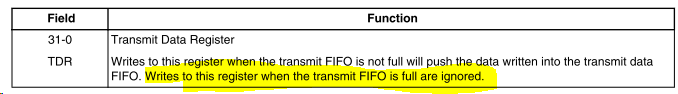

TX FIFO can underrun, RX FIFO can overflow. But TX FIFO can't overflow and RX FIFO can't underrun.

If DMA is used for TX FIFO and there's no empty space in the FIFO, the DMA request is simply not asserted. It's asserted only when the FIFO is not full.

Regards,

Lukas

Hi Lukas,

Can TX FIFO overflow, when e.g. watermark is set to 1 and DMA transfer is set to 2x 4samples (each sample is 32-bit).

In this case DMA request would be generated by SAI when there is 1 word left in FIFO? Can DMA write 8 words before the last 1 sample leaves FIFO?

Thanks,

Jakub

Hi Jakub,

sorry, I somehow missed that question.

No, it's simply ignored. It's user responsibility to ensure that full FIFO is not written. If DMA is not used, it's necessary to confirm before each write that FIFO is not full. If DMA is used then DMA descriptor must be configured in a way that only one sample is written to FIFO per one HW request. Then it is ensured that full FIFO will not be written again because there will be no HW trigger in this case.

In other words, it's necessary to avoid this situation, not to handle the consequences.

Regards,

Lukas