- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: S32K146 and SBCFS6503

S32K146 and SBCFS6503

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S32K146 and SBCFS6503

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

When I power on the FS6503 ,It only lasts 1.3s then shuts down . Our team can only use it's debug mode now.

/* Determine if it is necessary to re-initialize main register set. */

status = FS65_GetMode(&sbcMode, &prevMode);

/* FSSM can be initialized only in INIT_FS. */

if (sbcMode == fs65ModeInit)

{

/* Initialize FSSM (fail-safe registers). */

status = FS65_WriteRegisters(userConfig->initFailSafeRegs, userConfig->initFailSafeRegsCount);/*When I change the value of register "initFailSafeRegs", the default value is always read out, indicating that I did not change successfully. If my SPI driver is OK, can you give me some Suggestions?*/

if (status != fs65StatusOk)

{

return fs65StatusError;

}

/* INIT_MAIN -> NORMAL_MODE. */

/* If INIT_INT config value is not defined, just read and write the register value. */

if (userConfig->initIntReg == NULL)

{

status = FS65_ReadRegister(FS65_M_INIT_INT_ADDR, &response);

if (status != fs65StatusOk)

{

return status;

}

initIntValue = response.readData;

}

else

{

initIntValue = *(userConfig->initIntReg);

}

status |= FS65_WriteRegister(FS65_M_INIT_INT_ADDR, initIntValue, NULL);

if (status != fs65StatusOk)

{

return status;

}

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello,

I have the same problem.Can you tell me how to deal with it.

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,jason.

My problem was delayed by something else, and I later found out that my SPI communication was faulty.Restart the problem today, have you solved the problem?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, jack.

My problem wasn't solved yet, I have something else to do, and continue to solve later, If you solve the problem, please tell me the solution, thank you!and so do I

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,jason。

Have you solved the problem yet?So far I've debugged two versions of the same problem.After modifying the register value of 6503, it reads out the default value, and I can't find the problem point at present.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please take a closer look at our AN5238 where you can find the recommended start-up SPI sequence (Chapter 14.2).

From your code above it is not clear how you initialize the device and periodically refresh the watchdog. Please note that the first watchdog refresh (0x4D when using a default LFSR value of 0xB2) must happen before INIT_FS timeout (256ms). Then you need to periodically refresh the watchdog during every open window of the window period (set using WD_WINDOW_3:0 bits). If you would not like to use watchdog, use WD disable (WD_WINDOW_3:0 = 0b0000) in INIT_FS phase (256 ms open window after releasing RSTB) and then close INIT_FS phase by 1 good WD refresh (0x4D when using a default LFSR value of 0xB2). Then no further watchdog refresh is necessary.

You might also find useful an example project available at Embedded SW: FS65/FS45 SW Driver | NXP

Best regards,

Tomas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello,Tomas Vaverka

I have checked the start-up SPI sequence (Chapter 14.2). But I have another problem. Under what circumstances is the register read by Fs6503 the default value, or under what circumstances the register is unreadable?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am afraid I do not understand your question. Could you please rephrase it or provide more details?

Best regards,

Tomas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What I want to express is that when I initialize FSSM, I modify the values of the individual registers in it. When I read back, the data I read is always the default value. Is it that I failed to modify or that fs6503 cannot modify the values of registers in which case, and this state is ignored by me。

static fs65_reg_config_value_t initFailSafeRegs[] =

{

{

FS65_FS_INIT_FS1B_TIMING_ADDR,

FS65_R_FS_FS1B_TIME_106_848MS,

FS65_R_FS_FS1B_TIME_MASK,

true

},

{

FS65_FS_INIT_SUPERVISOR_ADDR,

FS65_R_FS_FS1B_TIME_RANGE_X1 | FS65_R_FS_VAUX_5D_NORMAL | FS65_R_FS_VCCA_5D_NORMAL |

FS65_R_FS_VCORE_5D_NORMAL,

0x0FU,

true

},

{

FS65_FS_INIT_FAULT_ADDR,

FS65_R_FS_FLT_ERR_IMP_RSTB | FS65_R_FS_FS1B_CAN_IMPACT_RX_ONLY | FS65_R_FS_FLT_ERR_FS_INT3_FIN6,

0x0FU,

true

},

{

FS65_FS_INIT_FSSM_ADDR,

FS65_R_FS_RSTB_DURATION_10MS | FS65_R_FS_PS_HIGH | FS65_R_FS_IO_23_FS_NOT_SAFETY |

FS65_R_FS_IO_45_FS_NOT_SAFETY,

0x0FU,

true

},

{

FS65_FS_INIT_SF_IMPACT_ADDR,

FS65_R_FS_WD_IMPACT_RSTB | FS65_R_FS_DIS_8S_ENABLED | FS65_R_FS_TDLY_TDUR_DELAY,

0x0FU,

true

},

{

FS65_FS_WD_WINDOW_ADDR,

FS65_R_FS_WD_WINDOW_512MS,

0x0FU,

true

},

{

FS65_FS_WD_LFSR_ADDR,

FS65_WD_SEED_DEFAULT,

0xFFU,

false

},

{

FS65_FS_INIT_WD_CNT_ADDR,

FS65_R_FS_WD_CNT_RFR_6 | FS65_R_FS_WD_CNT_ERR_6,

0x0FU,

true

},

{

FS65_FS_INIT_VCORE_OVUV_IMPACT_ADDR,

FS65_R_FS_VCORE_FS_UV_FS0B | FS65_R_FS_VCORE_FS_OV_RSTB_FS0B,

0x0FU,

true

},

{

FS65_FS_INIT_VCCA_OVUV_IMPACT_ADDR,

FS65_R_FS_VCCA_FS_UV_FS0B | FS65_R_FS_VCCA_FS_OV_RSTB_FS0B,

0x0FU,

true

},

{

FS65_FS_INIT_VAUX_OVUV_IMPACT_ADDR,

FS65_R_FS_VAUX_FS_UV_FS0B | FS65_R_FS_VAUX_FS_OV_RSTB_FS0B,

0x0FU,

true

}

};

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please close the INIT_FS phase by 1 good WD refresh (0x4D when using a default LFSR value of 0xB2). Then read back the INIT FS registers.

Best regards,

Tomas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Tomas

I tried to test it the way you said, but nothing worked.My SBC has not entered the LPOFF state, and I can't find any method. The "FS65_driver" is the driver package provided by you, and the "start-up SPI sequence" is good.

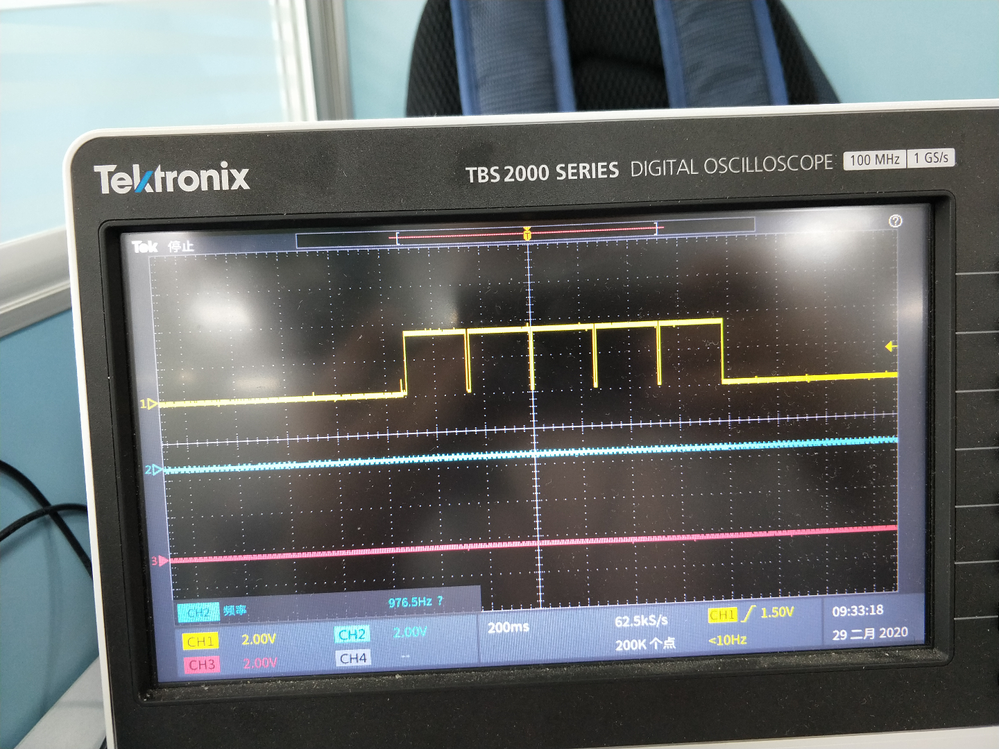

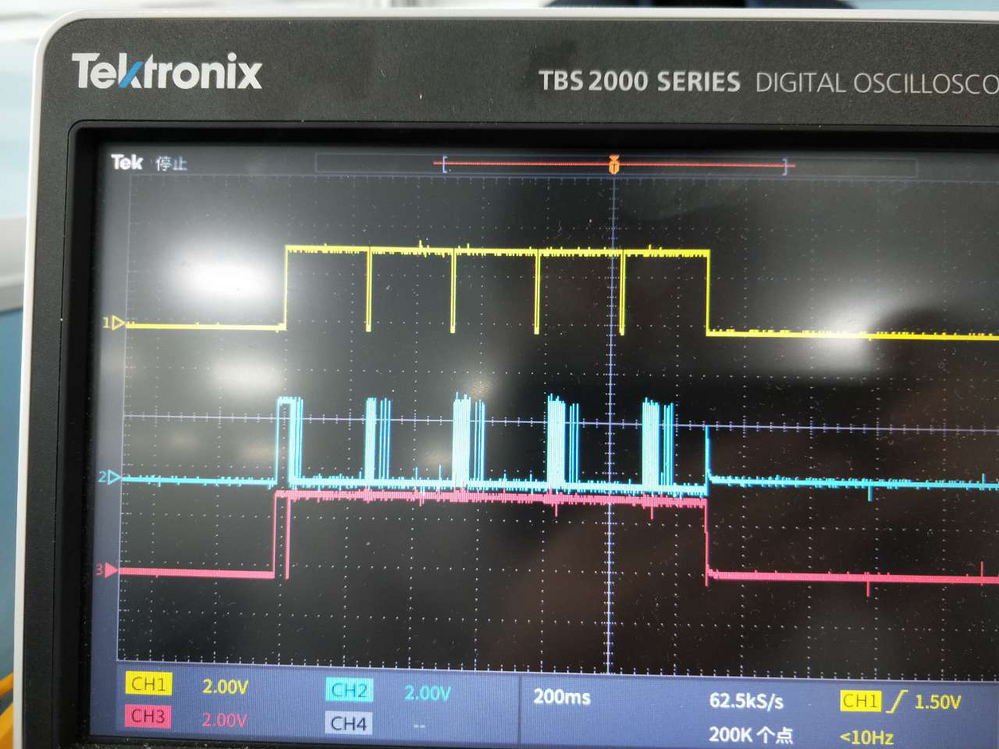

This picture is the pin of the reset tube of SBC. There are four times of reset at the moment of power supply, and the reset time is 4ms. May I ask whether this reset signal is unique to power supply of SBC itself, or is it caused by my hardware?I now read the SBC register value is the default value, is it related to this?

Now I see a problem. In INIT_FS mode, my FSSM did not write successfully.The above figure shows the reset pin in yellow, MOSI in blue and MISO in red. Why?