- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: S32K144 multiple interrupt enable

S32K144 multiple interrupt enable

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S32K144 multiple interrupt enable

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am trying to enable multiple interrupts one after the other, but only one interrupt which is enabled first is activated.

Please find below the snippet of the code (in this case only LPIT0 is interrupt is generated)

void NVIC_IRQs_Init (void)

{

S32_NVIC->ICPR[1] = 1 << (48 % 32); /* IRQ48-LPIT0 ch0: clr any pending IRQ*/

S32_NVIC->ISER[1] = 1 << (48 % 32); /* IRQ48-LPIT0 ch0: enable IRQ */

S32_NVIC->IP[48] = 0x3; /* IRQ48-LPIT0 ch0: priority 0 of 0-15*/

S32_NVIC->ICPR[1] |= (1 << (33 % 32)); /* IRQ33-LPUART ch1: clr any pending IRQ*/

S32_NVIC->ISER[1] |= (1 << (33 % 32)); /* IRQ33-LPUART ch1: enable IRQ */

S32_NVIC->IP[33] = 0x1; /* IRQ33-LPUART ch1: priority 2 of 0-15*/

}

void LPIT0_Ch0_IRQHandler (void)

{

LPIT0->MSR |= LPIT_MSR_TIF0_MASK; /* Clear LPIT0 timer flag 0 */

/* Perform read-after-write to ensure flag clears before ISR exit */

}

void LPUART1_RxTx_IRQHandler (void)

{

char receive;

if(LPUART1->STAT & LPUART_STAT_RDRF_MASK)

{

receive= LPUART1->DATA; /* Read received data*/

}

while((LPUART1->STAT & LPUART_STAT_TDRE_MASK)>>LPUART_STAT_TDRE_SHIFT==0);

}

If i initialize UART interrupt only, then UART interrupt will be activated.

PN: Designed with the help of S32K cookbook

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for the answer Daniel.

That wasn't also clear to me.

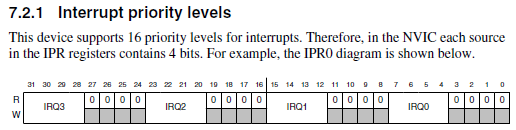

Referring to the Handbook :

FSL_NVIC->IP[48] =0x0A; /* IRQ48-LPIT0 ch0: priority 10 of 0-15*/

==> The priority level actually here is 2 not 10.

Is mu understanding correct ?

BR,

nicolas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Nicolas.

The priority number would be 0 in this case.

If you want to set priority number 2, it would be:

S32_NVIC->IP[48] = 0x20; (0b00100000)

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello pradeep.aithal@in.bosch.com,

The NVIC_IRQs_Init() function only clear the NVIC pending flags of the two interrupts and enables them, it seems to be correct, but there is no need to use the read-modify-write operation.

Is it possible that the application is in the LPIT ISR the whole time?

Because the priorities are not set correctly.

The number must be written to the 4 MSB of the IP registers.

So, your configuration sets the priorities of the two interrupts to 0 (highest).

If you expect the UART interrupt to preempt the LPIT interrupt, this won't work.

Can you share the project?

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

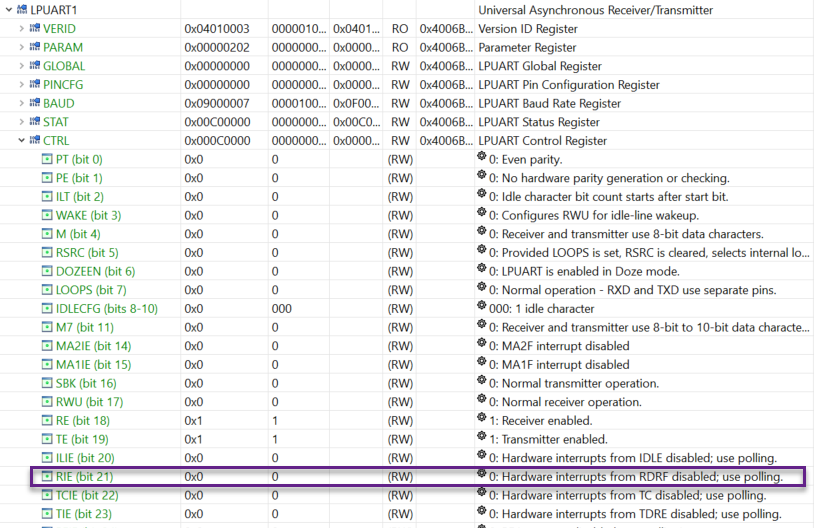

Dear Pradeep Aithal,

I have just tested the example, the NVIC module is set correctly except for the IP priority registers.

I understand you want to trigger the LPUART1 receive interrupt but it is not enabled in the LPUART1 module:

BR, Daniel