- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

Rise time and fall time requirement for S32K3 LPSPI Clock

Hi,

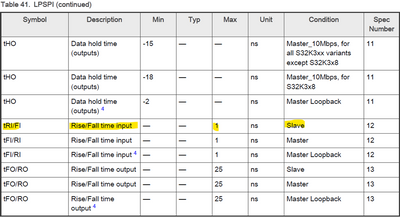

I am shanjai kanna from HCL. We are simulating SPI interface of S32K342NHT0MPBSR with another SoC FPGA. Here, SoC FPGA act as master and NXP S32K3 act as slave. While checking rise time and fall time for SPI Clock, they are greater than NXP S32K3 requirement (i.e.1ns). I am attaching NXP S32K3 rise time/fall time requirement in below image. We are getting 1.697ns rise time and 1.364ns fall time. Is it okay to get 0.697ns rise time and 0.364ns fall time more than NXP S32K3 requirement?

Thanks,

Shanjai kanna S

Hi @Shanjai,

The Rise/Fall time is measured with respect to 20% VDD_HV_A/B and 80% VDD_HV_A/B thresholds.

How do you measure the slew rate in your setup?

The 1ns specification simply says that the LPSPI has been validated at 1ns input signal - at slower rise/fall time, NXP does not guarantee the other LPSPI specifications.

It means the LPSPI does not require a specific rise/fall time as long as the other specifications are met (input setup, input hold, valid output, etc).

Regards,

Daniel

Hi @danielmartynek , We also measured with respect to 20% VDD_HV_A/B and 80% VDD_HV_A/B thresholds. We done timing analysis (Setup time and hold time) for LPSPI and met with input setup time and input hold time specifications. Is it okay?

Thanks,

Shanjai kanna S

Hi @Shanjai,

We don't have the LPSPI validated at a different input signal.

It is the user responsibility to ensure all the other requirements are met at a different input signal.

The input slew rate gets more important at higher baudrates.

Regards,

Daniel