- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: LPSPI CFGR1[NOSTALL] effect on Rx FIFO

LPSPI CFGR1[NOSTALL] effect on Rx FIFO

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

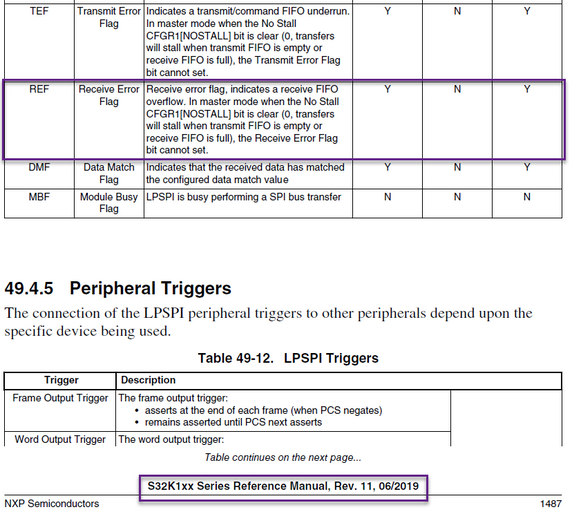

I noticed that when an Rx-FIFO overrun occurs, and thus SR[REF] is high, SPI transfers are stalled if CFGR1[NOSTALL] = '0'. Setting NOSTALL = '1' allows transfers to occur, even if REF = '1'.

When I reference S32K1xx Series Reference Manual, Rev. 12.1, 02/2020, two things come to my mind:

1. The effect of Rx overrun on stalling transfers is not mentioned.

For SR[TEF], the RM clearly mentions that when TEF is set when NOSTALL = '0', transfers will stall:

Indicates a transmit/command FIFO underrun. In master mode when the No Stall CFGR1[NOSTALL] bit is clear (0, transfers will stall when transmit FIFO is empty), the Transmit Error Flag bit cannot set.

The description for REF does not mention such behaviour:

Receive error flag, indicates a receive FIFO overflow.

Simply following the documentation, I would not expect REF to impact SPI transfers and cause a stall.

2. The effect of NOSTALL on Rx overrun stalling is never specified.

For NOSTALL, the RM mentions:

In master mode, the LPSPI will stall transfers when the transmit FIFO is empty, ensuring that no transmit FIFO underrun can occur. Setting the No Stall bit will disable this functionality.

0b - Transfers will stall when the transmit FIFO is empty

1b - Transfers will not stall, allowing transmit FIFO underruns to occur

Again, only the effect of the transmit FIFO is explicitly described here. Reading this documentation, I still don't expect a stall when Rx has overrun.

I recently found S32K144 LPSPI getting stuck in "void LPSPI1_transmit_16bits (uint16_t send)" function which confirmed my suspicion that REF causes a stall, and that NOSTALL can override this behaviour.

Am I correct to assume that this is the intended device operation, and that the documentation is missing in the reference manual?

Kind regards,

Joey van Hummel

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Joey,

It was described in the rev.11 of the RM.

Let me find out why it was removed from Rev.12, the release notes does not mention that.

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel,

Thanks for confirming. I'm curious as to why it was removed, but for now I will assume the behaviour is intended.

Kind regards,

Joey

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Joey,

It was described in the rev.11 of the RM.

Let me find out why it was removed from Rev.12, the release notes does not mention that.

Regards,

Daniel