- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

S32G2 - Aurora Connector Interface

Hi,

In one of our development project, we are using NXP S32G2 processor and interfacing with Aurora Trace connector.

On layout point, placement of Aurora Trace connector and signals routing are meeting layout guidelines of Aurora Trace connector (AN12530).

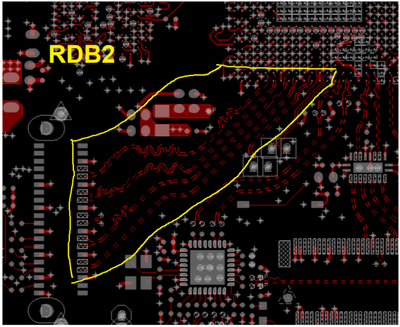

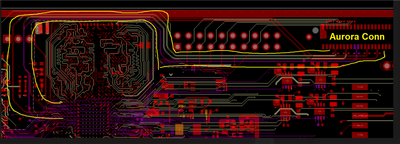

But not clear on length of differential pair. same is compare in RDB2 layout, it is ~1200mils, whereas in our PCB it is ~4500mils Max.

Here is the details about the PCB Layout:

1. No of layers : 10 layers

2. Signals (AUR_TXP2, AUR_TXN2) : Routed in layer 3

3. Signals (AUR_TXP0, AUR_TXN0) : Routed in layer 3

4. Signals (AUR_TXP1, AUR_TXN1) : Routed in layer 1 (Top Layer)

5. Signals (AUR_TXP3, AUR_TXN3) : Routed in layer 1 (Top Layer)

6. Signals (AUR_REF_CLKP, AUR_REF_CLKN) : Routed in layer 3

Attached the images of RDB2 and our PCB layouts for reference.

Query:

1. As signals length is high, Is there any effect on functionality of Aurora interface?.

2. Is it Okay, signals routed inner layers of layout and in multiple layers? (As per AN12530,Preferably on the top or bottom plane of the board).

3. Signal Integrity (SI) to be performed for Aurora signals?

Thank you.

Regards,

Gopala

Hi,

Below will be some comments on regards of your questions:

Q1. As signals length is high, Is there any effect on functionality of Aurora interface?.

A1 >> We are not seeing any restrictions on regards of length. If you are following the overall recommendations, you should not see problems with the communication. The constraint is on regards of the signal integrity itself.

Q2. Is it Okay, signals routed inner layers of layout and in multiple layers? (As per AN12530,Preferably on the top or bottom plane of the board).

A2 >> The following is told under the AN12530:

"The differential pair should be routed with a maximum of two vias. Ideally, the differential pair should be routed without vias on a single plane of the board (preferably on the top or bottom plane of the board). "

The ideal layout should be without transitions, hence all routed either on the top or bottom plane. If required, you cannot use more than 2 vias.

Q3. Signal Integrity (SI) to be performed for Aurora signals?

A3 >> Simulations are always useful when on the design process. If you follow all the constraints, you feel comfortable with the overall design, and you got some thumbs up from your design team, then you could skip the SI simulations, but doing them might still provide possible problems with the overall layout and show some improvements that could be made.

If it was for me, since you are mentioning some differences and if there might be any issues, I will recommend an SI simulation for confirmation of your design. Better be safe than sorry, in my opinion.

Please, let us know.