- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- S32G

- :

- [RDB2] PFE emac0&emac1 sending via SGMII on M7 is not working.

[RDB2] PFE emac0&emac1 sending via SGMII on M7 is not working.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

[RDB2] PFE emac0&emac1 sending via SGMII on M7 is not working.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, NXP support.

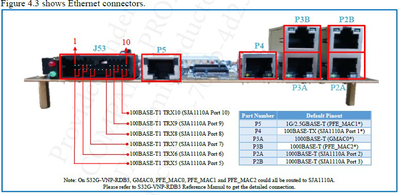

I'm using RDB2 board, M7 core running Vector CP + RTD(4.4_4.0.2) + PFE MCAL(v1.3.0) + PFE-FW(1.8.0), and I have already achieved the communication path: M7 - HIF0 - PFE_MAC2(RGMII) - P3B that is working properly.

Now my purpose is to utilize the Serdes_1 Mode3 to achieve the communication path: M7 - HIF0 - serdes_1(mode3) - PFE_MAC1(SGMII) - P5, but failed.

Some of my configurations on Eth&Mcu&Serdes as following:

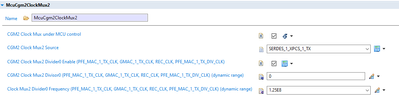

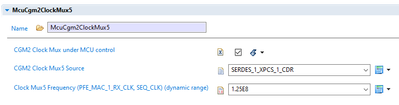

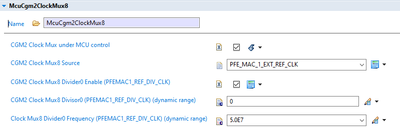

>Mcu: Mainly configure the clocks for PFE_MAC1 as followings:

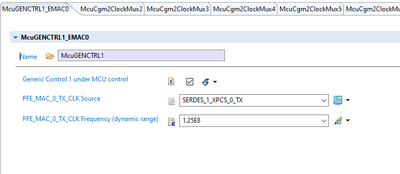

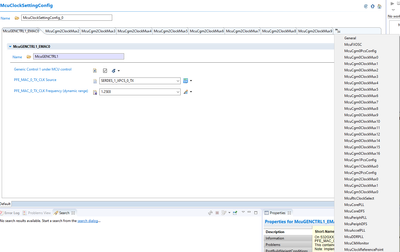

McuCgm2ClockMux2:

McuCgm2ClockMux5:

McuCgm2ClockMux8:

I didn't find the configuration for "McuGENCTRL1_EMAC1", only the "McuGENCTRL1_EMAC0"

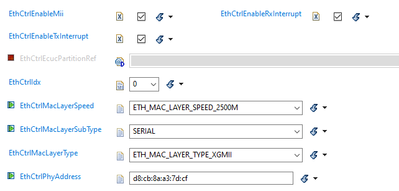

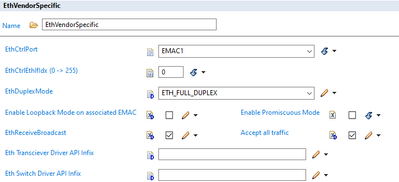

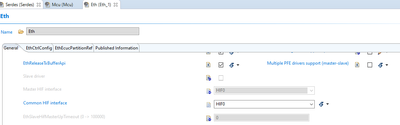

>Eth: the PFE_MAC1 I wonder to use SGMII 2.5G.

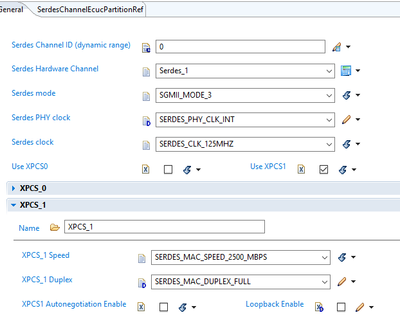

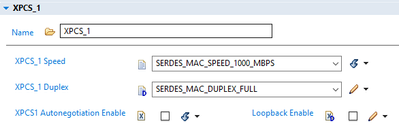

>Serdes: Choose Mode 3, XPCS1 for PFE_MAC1

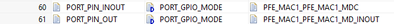

>Port: Configure the PHY MDIO port:

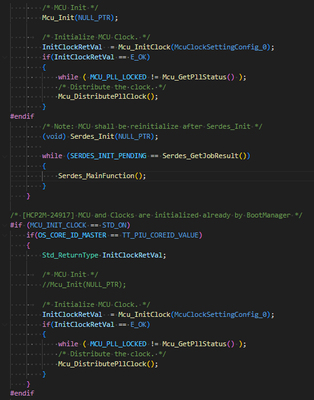

And for the Initialization, I have followed the guideline to perform Mcu clock initialization twice:

After above changes, in my program, I could see the Host is sending frames to PFE via registers. but nothing could see from the P5, also the ping is not working.

Could you please help to check what else is missing? or any wrong configuration?

"

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

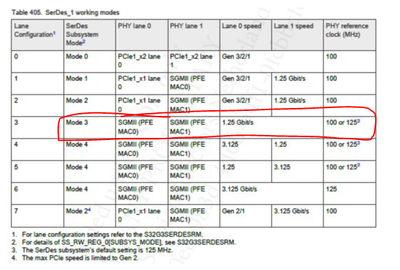

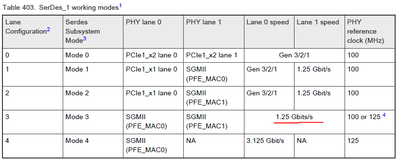

We will verify the information you are providing. We see that you are configuring XPCS_1 speed option as 2.5G, which is not available under the SerDes mode you are selecting (Mode 3). Under Mode 3, you need to configure the XPCS speed as 1Gpbs (for both channels, as shown under the SerDes_1 working modes) [S32G2 Reference Manual, Rev. 7, February 2023]:

Can you help us change the XPCS_1 Speed option to 1Gbps and verify if the behavior is the same?

As a comment, we see that you are using RDB3 documentation for an RDB2 board, which are similar but not the same. We can recommend looking into the RDB2 product page (link: S32G2 Vehicle Networking Reference Design | NXP Semiconductors) for more information on regards of RDB2 platform.

Please, let us know.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Daniel,

Thanks a lot for your feedback.

I followed your guidance to update the Rate to 1Gbps and got a different result.

What I made the changes are:

>On Serdes_1, change the Speed of XPCS_1 to 1Gbps.

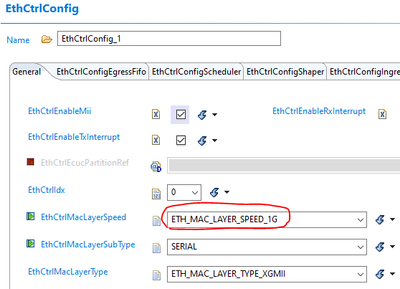

>On EthCtrlConfig. change the EthCtrlMacLayerSpeed to 1G.

After build&Flash.

The frames could be received by PFE_MAC1 from port "P5",

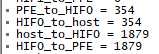

From the registers, I could see both directions statistics are increasing.

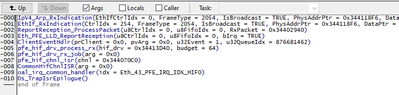

From the debugger, if I put the break point at "ARP indication callout" and then ping M7 address from Windows command line. I could see it has been hitted.

But, still I cannot see anything output from this RJ45 "P5" neither ping response, nor IPv4 frames.

So, it looks like, the PFE itself is working, the Rx path of SerDes_1 is working. but Tx path of SerDes_1 is not working.

Could you please help to check, if any clock or PHY controlling is missing or not configured correctly?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your feedback. We understand that at this moment the configuration seems to be right, but there is no communication under the RJ45 port, is this correct?

If so, help us verify that you are able to ping with P5 port under Linux following Chapter 6. PFE_MAC1(Connect to AQR113C or AQR107) Ethernet Enablement Guide available under the RDB2 product page (link: S32G2 Vehicle Networking Reference Design | NXP Semiconductors), to confirm that the PHY is working correctly.

Please, let us know.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Daniel, Thanks for your feedback.

"but there is no communication under the RJ45 port, is this correct?"

Yes, it's no communication, but not fully no communication...Actually, the Rx direction is working, but Tx direction is not working.

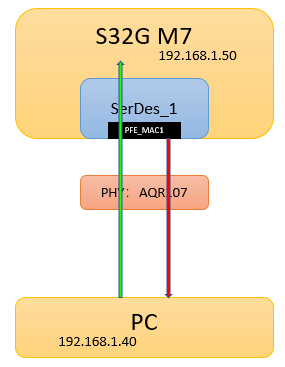

That means, when I ping 192.168.1.50 from PC, I could see the ping request has been received by S32G M7 core, and the ping response should have been reached "PFE_MAC1", but I cannot see the output from PHY(RJ45).

In my environment, the A53 only run a default QNX image, after startup, it will be blocked due to some reason, since currently I'm only focus on M7 core, the PFE driver is only run as a master without any slaves:

Is it possible to verify if the PHY is working correctly only from M7 core?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your feedback.

Since there is no example code available for the specific setup you are doing, we are unable to reproduce the issue you are seeing.

The available example is under Linux, which should let us know if everything is OK with the PHY, which is our main concern at this moment.

Please, let us know.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Danel

Thanks for your feedback

I maybe misunderstand your request.

I have thought you want to create the SD image combine My M7 image with the Linux BSP image.

Now I realized that you want me to flash the Linux example to test the connection.

So, I have download the Linux BSP28 from the website "binaries_auto_linux_bsp28.0_s32g274_pfe.tgz"

And get the SD image "fsl-image-auto-s32g274ardb2.sdcard" inside this package.

Then I flashed it into SD card by following command.

- cat /proc/partitions

- dd if=/dev/zero of=/dev/sdb bs=512 count=1 && sync

- cd /cygdrive/c/Conti_s32g/tool/RDB2/Step1/

- dd if=fsl-image-auto-s32g274ardb2.sdcard of=/dev/sdb bs=1M skip=4 seek=4 && sync

- dd if=fsl-image-auto-s32g274ardb2.sdcard of=/dev/sdb bs=1M count=4 && sync

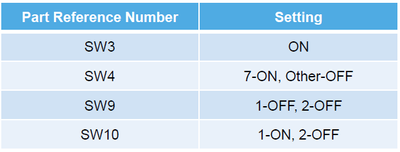

Next, I configure the "SW" as SD card boot mode:

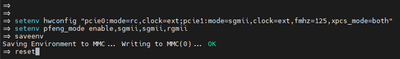

After inserting SD card into the board and power on, I followed the guideline in "S32G-VNP-RDB2 Ethernet Enablement Guide" Chapter 6 to set the variables under u-boot as below:

Finally, I configured the pfe1 ip and try to ping PC from RJ45 "P5":

So, the result is no response from PC, ping is not working.

Is this the things that you want me to verify?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your feedback and we apologize if our instructions were not clear from the beginning.

That is correct, we just wanted for you to replicate the example available under the Ethernet Enablement Guide to verify that everything was working.

For the results that you are sharing, seems to be that there is indeed a problem with the PHY. If you are able to move to a newer BSP version to double check the results could be great, but for further support, help us by contacting your local NXP FAE/DFAE/representative since seems to be a problem with the RDB2 bring-up on regards of the specific PHY, which seems to be missing FW related to it, or so we understand.

Please, let us know.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Daniel

Thanks a lot for your feedback.

I got it, I could like to check the PHY problem later.

Now I changed the PFE_MAC1 to be used as RGMII mode, which replace the GMAC0 channel.

I follow the guidance mentioned in "S32G_PFE_Master_Slave_Simple_Demo_V2_2023_5_23_Eng".

But the connection is not working, Ping is no response from RJ45(P3A)

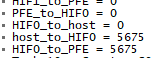

The register shows only have data from Host to PFE:

Since the PFE_MAC1 RGMII physical connection is quite similar with PFE_MAC2, I have verified the PFE_MAC2 is no problem, so not sure why the same configuration but not worked on PFE_MAC1.

Could you guide me if there are some special configurations requested on PFE_MAC1 as compared with PFE_MAC2?

Additional questions could you guide me:

>1. Do you have trace32 script(cmm) that could flash the SJA1110 on RDB2?(I found another guy has asked this question very long ago but no update, so double ask here)

>2. Could you guide me which document has introduced the method to create SD image combine the M7 image and A53 linux bsp image?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

It seems that we are misunderstanding this last request, if so we apologize.

Looking into the referenced documentation, we see that all modifications being talked about are on regards of PFE_MAC1, and given your comments it seems that the modifications being talked about are not working, is this correct? Which chapters have you followed? Since this demo works under PFE_MAC1-RGMII we understand that should be working no problem if followed correctly.

As for the questions, below will be some comments on their regard:

>1. Do you have trace32 script(cmm) that could flash the SJA1110 on RDB2?(I found another guy has asked this question very long ago but no update, so double ask here)

[NXP]: We understand that there is no *.cmm scripts provided by NXP aside from those available under the examples, which are S32G specific. On regards of the SJA1110, we can recommend contacting your local NXP FAE/DFAE/representative.

>2. Could you guide me which document has introduced the method to create SD image combine the M7 image and A53 linux bsp image?

[NXP]: We might not fully understand the question. On regards of multicore booting, we can recommend looking into AN13750 available under the S32G2 product page (link: S32G2 Safe and Secure Vehicle Network Processor | NXP Semiconductors).

Please, let us know.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, Daniel.

Thank you for your feedback.

I have followed the Chapter 3.5 in "S32G_PFE_Master_Slave_Simple_Demo_V2_2023_5_23_Eng.pdf".

And also, I checked the document "S32G_PFE_Demo_V2-2023.0320_Eng.pdf", Chapter 3.

These two documents mentioned the same configurations regarding to PFE_MAC1 on RGMII.

I double checked the configurations on Eth, Port and Mcu clock that make sure all have followed the guidelines.

But still the PFE_MAC1 is not working.

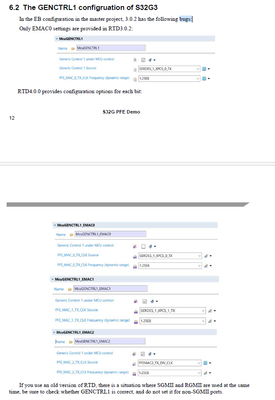

I found in "S32G_PFE_Demo_V2-2023.0320_Eng.pdf" Chapter 6.2, it has mentioned:

But in my EB configuration, I could only see the item "McuGENCTRL1_EMAC0" as below:

(The RTD I'm using is "SW32G_RTD_4.4_4.0.2" with plugin "Mcu_TS_T40D11M40I2R0".)

Is it still the bug mentioned above that "McuGENCTRL1_EMAC1" that cause the PFE_MAC1 not configured properly?

(For PFE_MAC2, even without the item "McuGENCTRL1_EMAC2" but it is no problem).

It's weird, as I mentioned in last comment, PFE_MAC2 with RGMII is quite similar with PFE_MAC1 with RGMII, result is PFE_MAC2 is working, but PFE_MAC1 is not working.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your feedback. Let us verify why it is not working. We will update you as soon as possible.

We apologize for any delay.

Please, let us know.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you confirm that the pinmux configuration is correctly done? Also, we can recommend opening a ticket under the NXP online services, since we might need to request your configuration project, for you to have a private channel.

Please, let us know.