- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- S32G

- :

- PFE MDC/MDIO PL_01 PL_02 erro

PFE MDC/MDIO PL_01 PL_02 erro

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

PFE MDC/MDIO PL_01 PL_02 erro

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

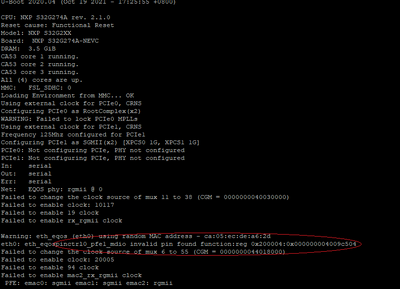

Because my design is different from the RDB Design, I use PL_01, PL_02 for the MDC/MDIO control pins of PFE1.

DTS configuration

/* PL01 */

#define PL01_MSCR_S32G (177)

#define PL01_PFE1_MDC_CFG (SIUL2_MSCR_S32_G1_MUX_ID_4 | \

MDC_PIN_CFG)

/* PL02 */

#define PL02_MSCR_S32G (178)

#define PL02_PFE1_MDIO_CFG (SIUL2_MSCR_S32_G1_MUX_ID_4 | \

MDIO_PIN_CFG)

#define PL02_PFE1_MDIO_IN (SIUL2_MSCR_S32_G1_MUX_ID_3)

2)uboot pfe1_mdio configuration in DTS

pinctrl0_pfe1_mdio: pinctrl0_pfe1_mdio {

fsl,pins = <PL01_MSCR_S32G PL01_PFE1_MDC_CFG

PL02_MSCR_S32G PL02_PFE1_MDIO_CFG

>;

};

When my Uboot is started, an error message is generated.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The problem has been solved Thank you very much

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Longfei,

I can't verify this here but could you find out what the configuration of the GMAC MDIO pins are if the GMAC is still in the device tree?