- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

LCU Configuration with 3 input and one LCU override

Hello Team,

I am working with an LCU module configuration with three input and one lcu override and one output as shown below

- For this 3 input and one lcu override how to perform the configuration, do we need to create separate LcuInputConfiguration containers for each input?

- Please give an idea on how to configure the input 2 (feed back from the output) and how to configure the lcu override.

- On what basis we are giving the values lcuLogicInput_MuxSelect for each input?

It will be appreciable if anyone can provide an example configuration and coding that will help this configuration.

Thanks and regards

Here I can only help you solve some problems in understanding the features of the LCU module.

If it is related to MBDT, you need to ask questions in the MBDT forum.

1.For this 3 input and one lcu override how to perform the configuration, do we need to create separate LcuInputConfiguration containers for each input?

An LCU is composed of 3 independent LC modules, each of which has four inputs and outputs. So according to the content of your picture, I think one LC is enough.

2.Please give an idea on how to configure the input 2 (feed back from the output) and how to configure the lcu override.

The output of LC can be directly selected as the input of LC, which I have highlighted in the picture.

Software Override is actually very simple. You can see the schematic diagram given in the data sheet. In fact, you only need to modify these two registers (I have highlighted them)

"To use software override, you must enable it for the corresponding output (SWEN[SWEN]). You assert software override by writing 1 to the corresponding bit of the Software Override Value" (SWVALUE[SWVALUE]).

3.On what basis we are giving the values lcuLogicInput_MuxSelect for each input?

I don't know how to explain this question better. its input needs to be based on your own needs.

The module input of LC can come from TRGMUX(or self), and the input of TRGMUX can come from many modules, such as external ports, eMIOS modules, etc.It's all depend on your needs.

For your know:

You can find the routines(Lcu_Ip_LcuControlMotor_S32K344) we provide for customers about the LCU module in S32 DS. In this routine, we also show the use of software override

Hello @Senlent ,

Thanks for your reply, its very helpful to understand software override

Regarding the third query i was asked about the mux select.

- Here we have so many mux values are available, so on what basis we select its value. In this figure i can see that 12 containers are created inside main container 'LCU Logic Input'(highlighted part), so do you have 12 inputs and created one container for each input? If so, on what basis we are selecting 'Mux Select' for each inputs?

- In my application, input one and two coming from trigmux LCU0_LC0_SEL0 and LCU0_LC0_SEL1 so what value of mux i can select for input one and two?

- Lcu_Ip_LcuControlMotor_S32K344 Where i can find the input details or schematic for this application. If the input and output connections are available then its better to understand the configuration easily

Thanks and regards,

Q1:Here we have so many mux values are available, so on what basis we select its value. In this figure i can see that 12 containers are created inside main container 'LCU Logic Input'(highlighted part), so do you have 12 inputs and created one container for each input? If so, on what basis we are selecting 'Mux Select' for each inputs?

You can see each LCU instance have three hardware logic cell which is :

LCU_IP_HW_LC_0, LCU_IP_HW_LC_1 and LCU_IP_HW_LC_3

each hardware logic have 4 input choice

For Mux Select:

LCU_IP_HW_LC_0 can choose :

LCU_IP_MUX_SEL_LU_IN_0 ~ LCU_IP_MUX_SEL_LU_IN_3

LCU_IP_HW_LC_1 ->

LCU_IP_MUX_SEL_LU_IN_4 ~ LCU_IP_MUX_SEL_LU_IN_7

LCU_IP_HW_LC_2 ->

LCU_IP_MUX_SEL_LU_IN_8 ~ LCU_IP_MUX_SEL_LU_IN_11

Q2:In my application, input one and two coming from trigmux LCU0_LC0_SEL0 and LCU0_LC0_SEL1 so what value of mux i can select for input one and two?

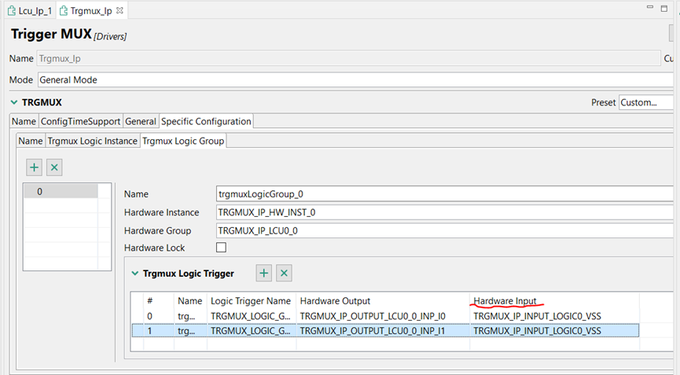

You should use TRGMUX module to select input source for LCU0_LC0_SEL0 and LCU0_LC0_SEL1.

("Hardware Input" depend on your needs and application.)

For example,Here i config LCU0_LC0_SEL0 and LCU0_LC0_SEL1 are both choose

TRGMUX_INPUT_LOGIC0_VSS as input source.

Q3.Lcu_Ip_LcuControlMotor_S32K344 Where i can find the input details or schematic for this application. If the input and output connections are available then its better to understand the configuration easily

This routine didn't add TRGMUX but only software way to control LCU input and output.

Regarding TRGMUX connect map, you can find it in our S32K3XXRM's attachments.

Hello @Senlent ,

I have few more doubts regarding LCU configuration settings and implementation.

1. As per our requirement we have to give one delay in LCU0_LC1 as shown below

How can we give this delay to LCU0_LC0, is it given through configuration or coding?

2. Regarding the coding part what all have the steps we follow?

- As per my understanding I have to initialize mcl and LCU , then Lcu_Ip_SetSyncInputSwOverrideValue() and Lcu_Ip_SetSyncInputSwOverrideEnable() for control SW override value,is this enough in coding part? all other functions will automatically run after the configuration, is my understanding correct? Do i need to remove or add anymore steps?

- we are already enabling the output in configuration so do we need Lcu_Ip_SetSyncOutputEnable() API in code?

Could you please look on my queries and reply your valuable suggestions and comments. Looking forward from you,

Thanks and regards

Q1.you can configurate it directly

Q2.From the picture your provided, you just need to init and enable the LCU out.

Lcu_Ip_Init(); /* initialize the LCU module */

Lcu_Ip_SetSyncOutputEnable(); /* Apply LCU output configuration */

Hello @Senlent ,

May i know how we can get the output status of LCU_LC whether its one or zero. I seen the function Lcu_Ip_GetSyncLogicOutput() when checked LCU document,

Currently i have given one array for my one output

Lcu_Ip_SyncOutputValueType LCU0_LC0_OutputList[1] =

{

{LCU_LOGIC_OUTPUT_1, FALSE},

};

then calling the following steps and functions

LCU0_LC0_OutputList[0U].Value = LCU_IP_OUTPUT_ENABLE;

Lcu_Ip_SetSyncOutputEnable(&LCU0_LC0_OutputList[0U], 1);

Lcu_Ip_GetSyncLogicOutput(LCU0_LC0_OutputList, 1);

As per my expectation i have to get value of 1 in the array LCU0_LC0_OutputList when the lcu out is one but i am getting zero there in the array.

Is this sufficient to check the lcu output status, if yes, could you please let me know the correct usage of this function.

please check this scenario and please support me with your feedback

Thanks and regards

Hi@emerging

There is nothing wrong with your usage

This API can get the output status of the LCU channel, but I don't see the input of your LCU module. If your LCU module has no input, then this result is not normal, right?

You can use an oscilloscope or multimeter to verify this API.

Hello @Senlent ,

I have given input and confirmed the output is one with multimeter, issue facing with this function to get the output value that's why i mentioned only the output related steps here in my question.

Thanks for your conformation Selent. I will cross check my implementation and try to dubug.

Thanks and Regards,

Hi @Senlent ,

I am very much thankful for your support. It will be more easy if i can share my project but i am not sure about it.

The above issue is resoved and my thanks for your support

But unfortunately i have one more block.

As you can see above i have two sw override in input pin 2 and 3 and i am able to control pin 2 in software by enabling sw override and i control the output as one and zero. But the second override with latch i am not able to control

I made the pin 2 as one with sw override and checked and confirmed the corresponding output is one and the output is latched to 3rd input,so even after i made the pin2 low the output is maintained as one because of output latch. Till this its working,but after i am trying to change the 3rd input pin as zero i am expecting my out will be zero because both the input 2 and three as zero. but unfortunately the output is keeping as one.

Here i am mention my configurations and code,

Configuration:

Below are the final step i used to control the pin 3 after latch:

Hi @Senlent ,

- Actually sw override means it override another input value. But here your point is, sw override can override all other inputs other than a latch input from an output.

- We can enable software override for each inputs separately

Could you please confirm my understanding is correct or not?

Thanks and regards