- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- Home

- :

- 製品フォーラム

- :

- S12 / MagniVマイクロコントローラ

- :

- Re: current loop

current loop

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

current loop

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

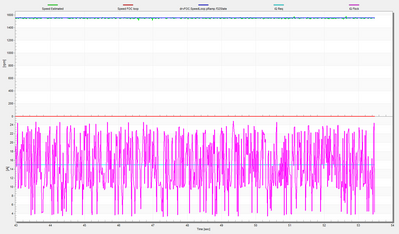

hello,

could you please help to check why Iq current has so big oscillation?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

What's your motor parameters and your MCAT configuration?

Is it a small Inductance motor? if yes, you may need increase the foc frequency. for example, from 20kHz to 25kHz.

if not, general speaking, you can decrease the current loop frequency, for example, 150Hz. if it still not optimized,

the another cause may related with your current sampling hardware.

you can verify the current sampling quality by monitor the phase current ABC when motor is stopped.

hope helps,

regards,

Raymond

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I used S12ZVML128, the single shut resistance sampling. I could run motor in open loop.

I checked the Iq has big oscillation, it couldn’t switch to close loop.

Resistance and induction are very small.

Rs = 0.05ohm

Ld = 40uH

Lq = 60uH

BEMF = 3V@1000RPM

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

the inductance is small, but L/R is still in normal range.

What's your current loop F0 and your FOC frequency?

would you paste the angle scope of FreeMASTER in tracking mode?

or would you upload your motor parameter file?

you can do current loop diagnose, set a step current command, for example 2A, and then monitor the current response to check whether the loop F0 is suitable or not. If the real current response is lag the command obviously, you can increase the F0, if it response will overshot the command, you can decrease the F0.

hope it helps,

Raymond

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Are you using the external bus votlage divide circuit? the Umax is 36.0F, not default 25V.

for the following parameter:

#define MERG_SPEED_1_TRH FRAC16(0.2500000000)

#define MERG_SPEED_2_TRH FRAC16(0.2666666667)

the merge speed 1 should be around 5% of rated speed, and speed 2 can be 7% ro 10% rated speed. after reach the speed1, observer will work and track the rotor position, but the FOC not use the observer angle, after the speed2, it will use the observer output.

keep a gap for speed1 and speed2.

Best regards,

Raymond

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Peter,

please provide much more details.

Best Regards,

Stano.