- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- 产品论坛

- :

- S12 / MagniV微控制器

- :

- CW12 V3.1 - New Installation, Build Errors for Supplied Beans

CW12 V3.1 - New Installation, Build Errors for Supplied Beans

CW12 V3.1 - New Installation, Build Errors for Supplied Beans

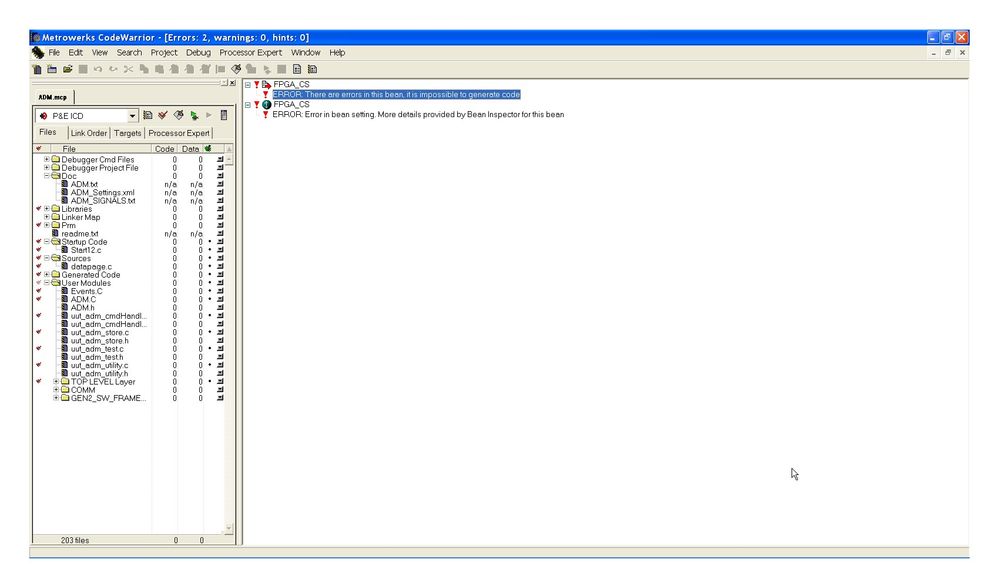

I am new to my position. This company has an older product that was developed under CodeWarrior for MC9S12E128.I installed CW12 v3.1 and when I went to build the project taken from source control, I got 4 build errors all to do with supplied beans. I have attached a screenshot of the build report. Since it's a new installation, there might be some configuration I need to make in order for the beans to compile. If someone can point me in the right direction I would appreciate it!

Andy McNeil | Systems Engineer

Spotwave Wireless Inc.

Kavveri Telecom Products Limited

P.O. Box 550

500 Van Buren Street

Kemptville, ON K0G 1J0

CANADA

T 613.591.1662 ext. 3336

F 613.258.7418

Thank you Radek, your answer was what I was looking for. It reduced my build errors from 4 down to 2. it's really one error now as both errors are to do with the same bean. Since the errors were to do with beans, it meant I was either missing something or not configuring Processor Expert correctly.

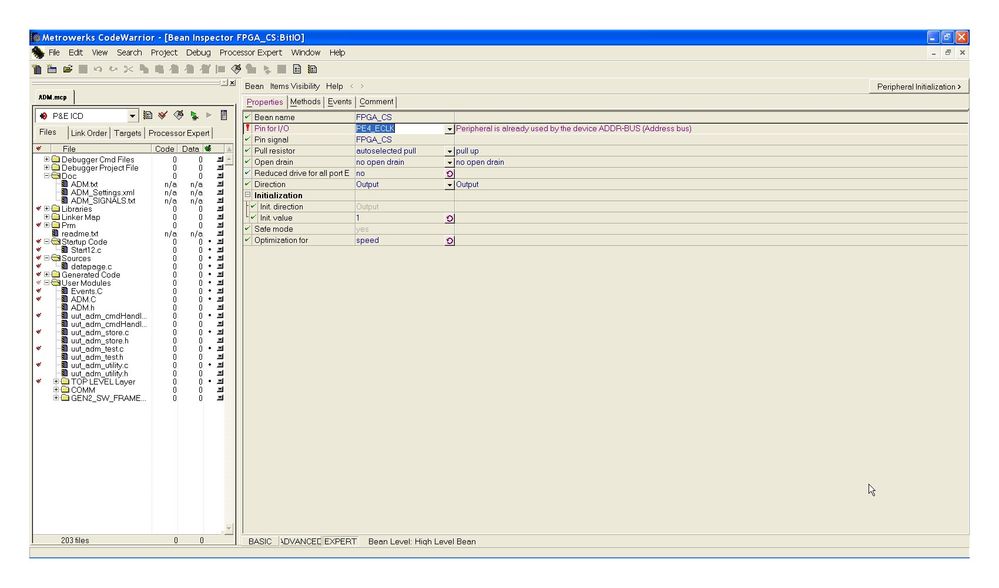

I am keeping this thread open until I solve the remaining bean error. Latest screenshot of build report below.

In all modes except Normal Single Chip Mode, the PE4 pin is initially configured as the output connection for the internal bus clock (ECLK).

PE4 - Bus timing reference clock, can operate as a free-running clock at the system clock rate or to produce one low-high clock per visible access in expanded modes, with the high period stretched for slow accesses (ECLK is used as a timing reference and to demultiplex the address and data).

The ECLK frequency is equal to 1/2 the crystal frequency out of reset.

The ECLK output function depends upon the settings of the NECLK bit in the PEAR register, the IVIS bit in the MODE register and the ESTR bit in the EBICTL register.

So, everything depends on your hardware/software settings.

In Normal Single Chip Mode, PE4 works as GPIO until you clear NECLK bit in the PEAR register.

In Special Single Chip Mode, PE4 works as bus clock output. This is very good toll for debugging purposes.

In expanded modes, PE4 is used as a timing reference for external memory.

Please look at your hardware configuration (if ECLK signal is necessary) and PEAR_NECLK bit.