- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- 产品论坛

- :

- S12 / MagniV微控制器

- :

- Re: About S12Z ADC sample time and interrupt

About S12Z ADC sample time and interrupt

About S12Z ADC sample time and interrupt

1.ADC saple time

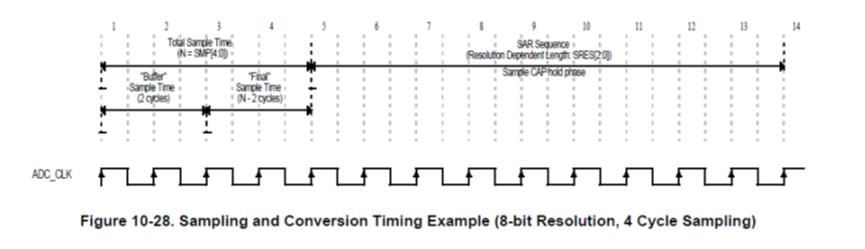

the above figure as the example ,8-bit data,4 cycle sampling , the adc min sampling time=?

the adc sampling time =adc clock/12 or 13? if is 13,why?

2.ADC Interrupt

If I want trigger the adc interrupt by timer0,every 50ms sample the data 100times by AN3,how to do it ?

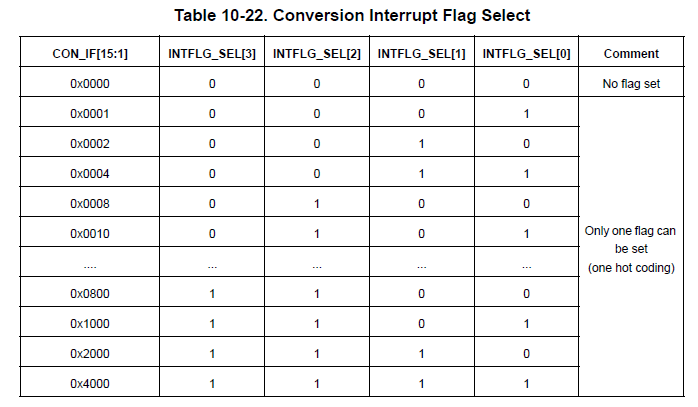

The INTFLG[3:0] is to configure the interrupt flag number(1~15),the interrupt flag number is defined by myself? If I want to sample the AN3,can I set the interrupe flag number is 1 or 2,...?

Hello jx1207@126.com,

1.

You didn’t specify the MagniV device.

Let’s take S12ZVL.

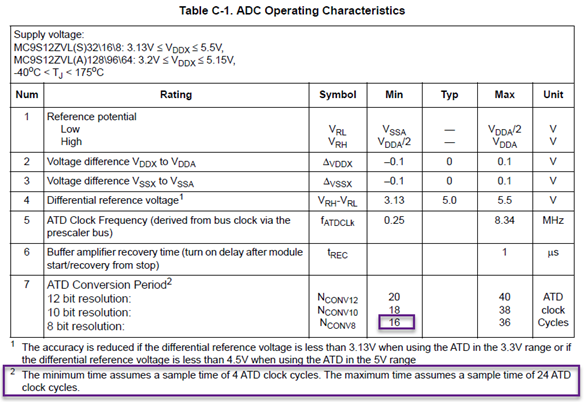

The ATD conversion time is specified in Table C-1, S12ZVL RM rev2.48

In the Figure 28-10 example:

Sample time: 4 ATD clock cycles

Hold time: 12 ATD clock cycles

Conversion time: 16 ATD clock cycles.

2.

Please have a look at Example S12ZVL ADC0 triggered by TIM0 OC updates PWM duty cycle

It uses TIM0 Output Capture on Ch2 to trigger an ADC sequence periodically.

Please see the description of the ADC command registers in the RM.

In ADCCMD_1[CH_SEL[5:0]] you can select AN3.

In ADCCMD_0[INTFLG_SEL[3:0]] you can select which interrupt flag is set in the ADCIFH/L register

at the end of this conversion.

Regards,

Daniel