- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- Home

- :

- QorIQ Processing Platforms

- :

- QorIQ

- :

- T2080QDS Secure Boot

T2080QDS Secure Boot

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

T2080QDS Secure Boot

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I been trying to activate the secure boot on the platform for a while now.

I followed the following instructions:

1) QORIQ-SDK-2.0-IC-REV0_T1_T2_T4 Secure Boot demo.

2) Setting up Secure Boot on PBL Based Platforms in Prototype Stage.

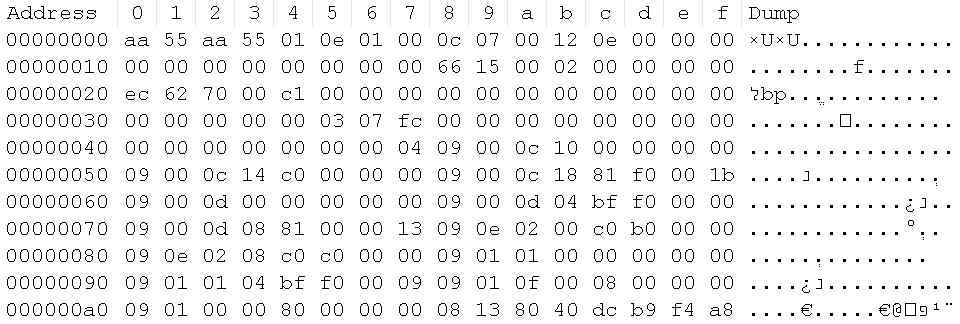

For writing the SRK i used lauterbach, attached are the values of SECMON and SFP registers after the core release.

I receive no prints to the console, please advice me how to continue.

Thanks,

Ilya German

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Please review the steps i made to permenently write the OTPMK registers on t2080QDS:

1) Enable POVDD SW9[8] = 0x1.

2) Short PROG_SFP(J27) jumper.

3) Write OTPMK to mirror registers 0xfe0e821c - 0xfe0e8238.

4) Permenantly write the OTPMK to fuze 0xfe0e8020 = 0x2.

Did i miss anything ?

Thanks,

Ilya

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Ilya German,

Please refer to the following recommended troubleshooting actions when No print on UART console.

1. Check the status register of sec mon block (location 0xfe314014). Refer to the details of the register from the Reference Manual. Bits OTPMK_ZERO, OTMPK_SYNDROME and PE should be 0 otherwise there is some error in the OTPMK fuse blown by you.

2. If OTMPK fuse is correct (see Step 1), check the SCRATCHRW2 register for errors. Refer to Section for error codes.

3. If Error code = 0 then check the Security Monitor state in HPSR register of Sec Mon.

Sec Mon in Check State (0x9)

If ITS fuse = 1, then it means ISBC code has reset the board. This may

be due to the following reasons:

Hash of the public key used to sign the ESBC u-boot doesn't match with the value in SRK Hash Fuse

Or

Signature verification of the image failed

Sec Mon in Trusted State (0xd) or Non Secure State (0xb)

Check the entry point field in the ESBC header. It should be 0xcffffffc for the demo.

If entry point is correct, ensure that u-boot image has been compiled with the required secure boot configuration.

In your attachment HPSR is 8000a900, OTPMK_ZERO, OTMPK_SYNDROME and PE files of HPSR is zero, SCRATCHRW2 is zero, HPSR[SSM_ST] is 9, please refer to the proper reason.

If ITS fuse = 1, then it means ISBC code has reset the board. This may

be due to the following reasons:

Hash of the public key used to sign the ESBC u-boot doesn't match with the value in SRK Hash Fuse

Or

Signature verification of the image failed

Thanks,

Yiping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for the quick response !

The ITS fuse = 0, thats weird because i used RCW with SB_EN = 1 and BOOT_HO = 1(See attached file).

Do you have any idea why the ITS fuse equals 0 ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Ilya German,

In prototype stage, ITS fuse should be 0. Please refer to the section " Deploy Secure Boot Images to the Target and Write SRKH Mirror Register" inSetting up Secure Boot on PBL Based Platforms in Prototype Stage

You need to permanently write OTPMK key into fuse array.

Thanks,

Yiping