- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

I am facing an issue related to PCIe configuration on T1042 Power PC, which is configured as an endpoint

Initially my design was working fine with one lane PCIe with 32 bit 2 GB DDR3L, now design has some changes I am looking to configure 4 lane PCIe with 64 bit 4 GB DDR3L.

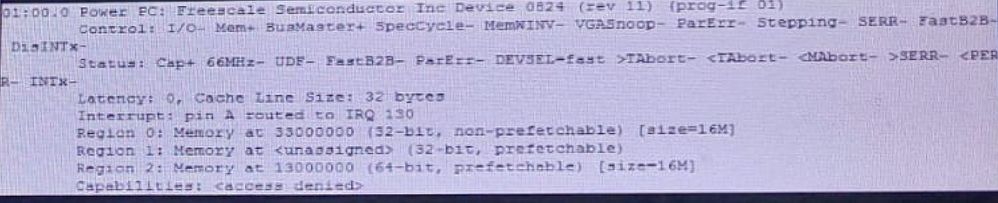

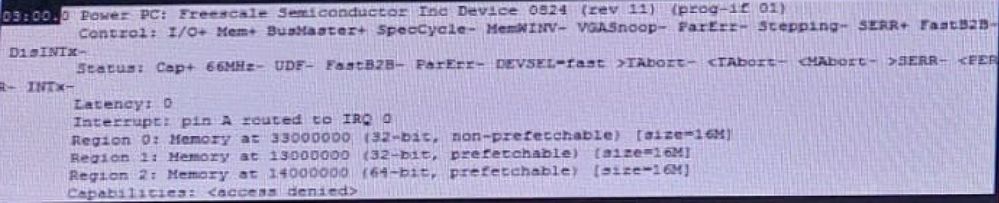

Output of lspci -vv command on root-complex device gives an unassigned memory in second case. It states BAR addresses to be unassigned.

Comparing from the previous setup output of same command, BAR0 is assigned correctly, while for BAR1 it gives unassigned memory and

for BAR2 it is swapped with the memory assigned to BAR1 in previous case

Below I have attached outputs of both designs

Does anyone know how to solve this issue

@yipingwang Can you please help. You have solved most my problems earlier too.

已解决! 转到解答。

thanks @ufedor for your kind help. We could not find where this register value was being set, so we hard-coded it.

Now it is working perfectly. Thank you for time and help.

Regards Ather

Thanks @ufedor for your prompt reply. Attached are the files that you have requested.

T1042rdb_v1_bootprints.txt represents Old configuration

T1042rdb_v2_bootprints.txt represents new configuration

Regards

Ather

> I am looking to configure 4 lane PCIe

The same SerDes protocols are used in both configurations and it has PCIe1 x4 trained to x1 Gen1 - i.e. no difference.

Please provide additional information:

1) Output of lspci -vv command on RC device as text files

2) DTS files which are used in both configurations

Here are the files that you have requested.

Dts files were same in both cases

Yes same dts is used in both cases.

bus number is changed because in previous version we were using a PCIe bridge that connects one root complex to two PCIe endpoint out which one endpoint is our T1042. However, in newer version we removed that PCIe bridge and directly connected root complex with endpoint(T1042).

It is because we have removed capacitors from series path of lane 2, 3 and 4. Hence the only established connection is of single lane PCIe, which must not be a problem since PCIe can downstream itself depending upon the connections.

Also this is done only for debugging purpose.

V1

fe240dc0: 0007e000 00000000 00000000 00000000 ................

fe240dd0: a0f55017 00000000 00000000 00000000 ..P.............

V2

fe240dc0: 000fdff0 00000000 00000000 00000000 ................

fe240dd0: a0f5501f 00000000 00000000 00000000 ..P.............

Why is this difference?

This was changed in drivers file for DDR changes (from 2Gb to 4Gb). I thought this change would fix the memory unassigned issue as we assumed that for 4gb ddr we have to set registers accordingly, but it didn't. Forgot to revert the changes. What do you propose I should have done?