- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- ソフトウェア・フォーラム

- :

- プロセッサ・エキスパート・ソフトウェア

- :

- Re: IMX6SOLO MX6QDL_PAD_DI0_PIN2__IPU1_DI0_PIN02 PULL DOWN in U-Boot

IMX6SOLO MX6QDL_PAD_DI0_PIN2__IPU1_DI0_PIN02 PULL DOWN in U-Boot

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

IMX6SOLO MX6QDL_PAD_DI0_PIN2__IPU1_DI0_PIN02 PULL DOWN in U-Boot

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I Want to set this pin in pull down mode during u-boot phase start-up to respect the display sequence power on. When I measure the signal, directly at the output of the PIN, it is in pull up state.

You can find here my u-boot dtsi configuration :

&iomuxc {

u-boot,dm-pre-proper;

pinctrl-names = "default";

pinctrl-0 = <&BOARD_InitPins>;

imx6s-board {

BOARD_InitPins: BOARD_InitPinsgrp { /*!< Function assigned for the core: Cortex-A9[ca9] */

fsl,pins = <

MX6QDL_PAD_EIM_DA0__SRC_BOOT_CFG00 0x0000B0B1

MX6QDL_PAD_EIM_DA1__SRC_BOOT_CFG01 0x0000B0B1

......

/*RGB PINS*/

......

MX6QDL_PAD_DI0_PIN2__IPU1_DI0_PIN02 0x000130B0

........

};

};

If you have any idea.

Thank you for the help

Guillaume

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

To set the pin in pull-down mode during U-Boot phase startup, modify the value of MX6QDL_PAD_DI0_PIN2__IPU1_DI0_PIN02 in the BOARD_InitPins section of your dtsi file from 0x000130B0 to 0x000120B0. Recompile and update the device tree binary (dtb) file for the changes to take effect. Let me know if you have more questions. Carports

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

suggest to connect jtag debugger and toggle pin (configure as gpio), probably it is shorted to

other signal. Bedside Tables

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Guillaume

dtsi configuration looks as correct, reason may be that lcd has internally more strong pull-up

resistor than i.MX6S 100K Ohm pull down.

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I made the test without the screen plugged, so without any possible pull up resistor connected to the screen, The signal output is pull up even with the screen not plugged.

Guillaume

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

suggest to connect jtag debugger and toggle pin (configure as gpio), probably it is shorted to

other signal.

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Igor,

I forgot to mention that the screen is operational.

The images are displayed correctly on the screen. It is only when u-boot starts that the HSYNC signal is high and this affects the screen's power-on sequence. We also have the same problem on another processor: IMX6ULL. The routing of the board is correct.

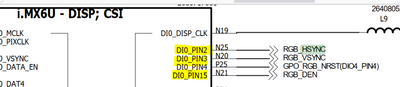

Three signals are in bad state at boot time (during u-boot) DI0_PIN2 (HSYNC), DI0_PIN3 VSYNC, and DI0_PIN15 (RGB_DEN). All these pins must be in pull down mode but they are pull up.

These 3 pins are configured in pull down mode in u-boot in the iomuxc node:

&iomuxc {

u-boot,dm-pre-proper;

pinctrl-names = "default";

pinctrl-0 = <&BOARD_InitPins>;

imx6s-board {

BOARD_InitPins: BOARD_InitPinsgrp { /*!< Function assigned for the core: Cortex-A9[ca9] */

fsl,pins = <

MX6QDL_PAD_EIM_DA0__SRC_BOOT_CFG00 0x0000B0B1

.......

MX6QDL_PAD_DI0_DISP_CLK__IPU1_DI0_DISP_CLK 0x000130B0

MX6QDL_PAD_DI0_PIN2__IPU1_DI0_PIN02 0x000130B0

MX6QDL_PAD_DI0_PIN3__IPU1_DI0_PIN03 0x000130B0

MX6QDL_PAD_DI0_PIN15__IPU1_DI0_PIN15 0x000130B0

>;

};

Best regards

Guillaume

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you for the answer.