- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- 软件论坛

- :

- Processor Expert软件

- :

- Re: Configuration problem with fsl_sdcard driver component

Configuration problem with fsl_sdcard driver component

Hi,

I am trying to use the fsl_sdcard component with KDS 3.0.0 and PE, and the eval boards FDRM K22F and FRDM-KL25Z.

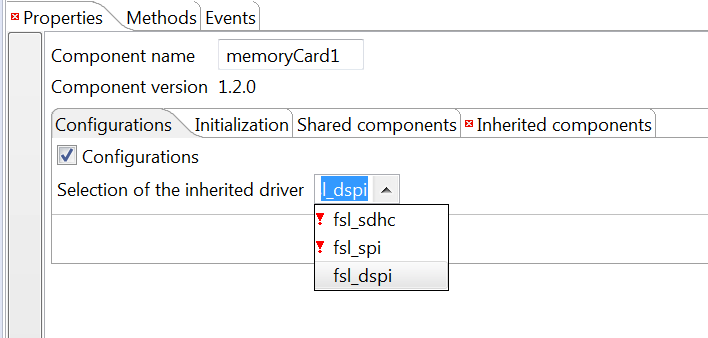

Using the FRDM-K22F, the inherited component is added:

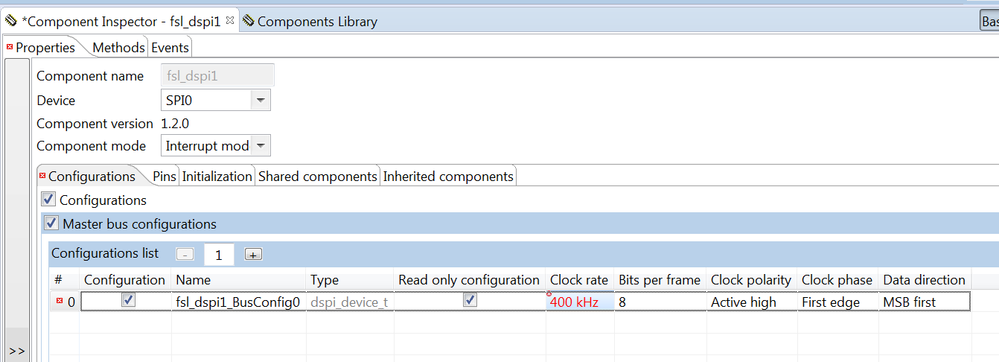

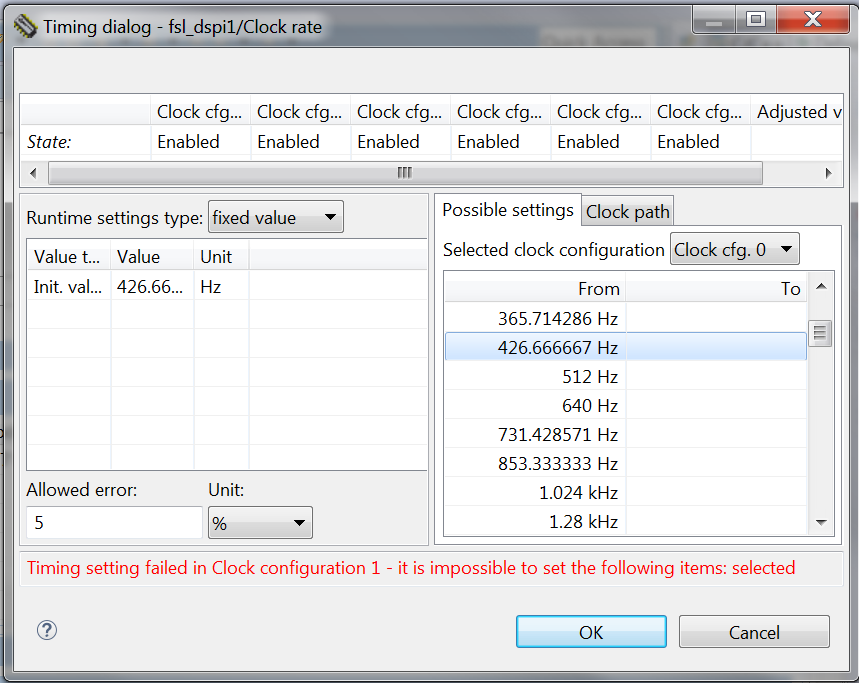

But a problem occurs in the fsl_dspi component. Is not accepted any clock value, like you can see in figure below:

Even using the timing dialogue box, to choose a predetermined clock, doesn't work:

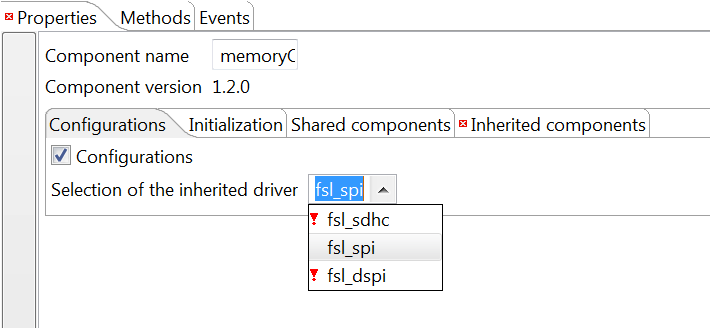

The same problem occurs using FRDM KL25Z, however, the inherited component add is the fsl_spi.

Any advice?

已解决! 转到解答。

Hello Matheus Pinto:

When you create a project for a board (e.g. FRDM-K22F) Processor Expert provides a set of predefined clock configurations. You can analyze such configurations by opening the settings of the fsl_clock_manager component.

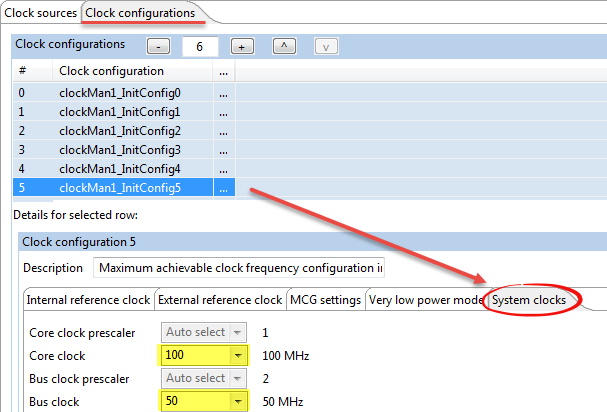

For example the "clockMan1_InitConfig5" corresponds to a Core clock = 100 Mhz and Bus clock = 50 MHz:

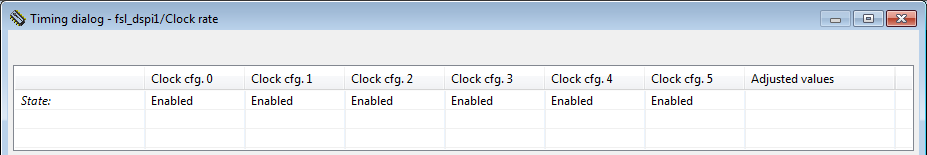

In the top of the timing dialog box for fsl_dspi you can see that all the clock configurations are enabled by default:

In that case the SPI clock frequency must be achievable with all clock configurations using dividers and prescalers.

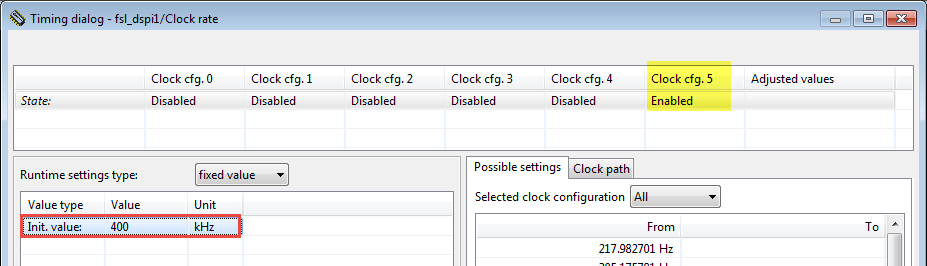

To resolve this you can simply disable the configurations that you will not use. e.g. I enabled only Clock cfg. 5 and this lets me set the frequency to 400 kHz:

I hope this helps. Let me know if you have questions.

Regards!,

Jorge Gonzalez

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hello Matheus Pinto:

When you create a project for a board (e.g. FRDM-K22F) Processor Expert provides a set of predefined clock configurations. You can analyze such configurations by opening the settings of the fsl_clock_manager component.

For example the "clockMan1_InitConfig5" corresponds to a Core clock = 100 Mhz and Bus clock = 50 MHz:

In the top of the timing dialog box for fsl_dspi you can see that all the clock configurations are enabled by default:

In that case the SPI clock frequency must be achievable with all clock configurations using dividers and prescalers.

To resolve this you can simply disable the configurations that you will not use. e.g. I enabled only Clock cfg. 5 and this lets me set the frequency to 400 kHz:

I hope this helps. Let me know if you have questions.

Regards!,

Jorge Gonzalez

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------