- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- Home

- :

- 产品论坛

- :

- 动力和电气化模拟驱动器

- :

- MC33HB2001 - Internal Pullups

MC33HB2001 - Internal Pullups

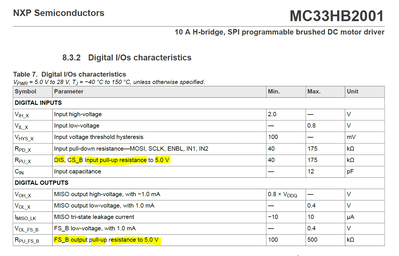

The datasheet indicates that the MC33HB2001 has internal pullups to 5V and I am questioning if this is correct when VDDQ of 3.3V is applied:

When looking at the development board FRDM-HB2001FEVM it looks like you can connect VRDM_VDD to VDD and VDD to VDDQ.

Could someone confirm if these internal pullups are to VDDQ or is there an internal 5V regulator?

已解决! 转到解答。

Hi David,

The pull-up level is dependent upon the voltage level applied to VDDQ. If 3.3V is applied on VDDQ, the internal pull-ups will be to 3.3V for these logic pins. I think the spec is referring to a 5.0V applied to VDDQ scenario.

Best regards,

Tomas

I have laid out a development board using the MC33HB2001FKR2. I supplied 12V to VPWR (pins 12,13,29,30) and 3.3V to VDDQ (pin 1) and CS_B (pin 32) measures to be 0V. According to the datasheet the CS_B pin should be internally pulled up. Can you confirm or deny? I confirm the same behavior on the NXP development board FRDM-HB2001FEVM.

Hi David,

Yes, CS_B has an internal weak pull-up to VDDQ. The FRDM-HB2001FEVM development board drives the SPI signals at 3.3V. The MCU should not be holding the CS_B pin low while data is not being transmitted.

Best regards,

Tomas

Hi David,

The pull-up level is dependent upon the voltage level applied to VDDQ. If 3.3V is applied on VDDQ, the internal pull-ups will be to 3.3V for these logic pins. I think the spec is referring to a 5.0V applied to VDDQ scenario.

Best regards,

Tomas