- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- RFID / NFC

- :

- NFC

- :

- [PN7462] HCE - phhalRf_AutoColl function does not activate ALM?

[PN7462] HCE - phhalRf_AutoColl function does not activate ALM?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

[PN7462] HCE - phhalRf_AutoColl function does not activate ALM?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi!

We would like to add a HCE mode to one of our PN7462 reader boards. Because the underlying schematic does not have the ANT-pins attached to the antenna we would like to use the Active Load Modulation-Feature (ALM) of the chip.

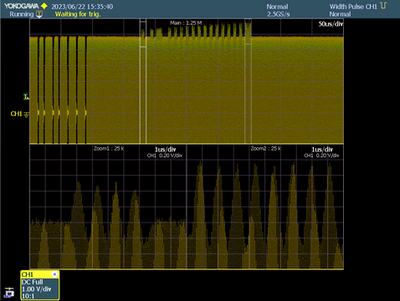

For a simple test I placed a CLRC663 eval board above the PN7462 reader board. In-between both devices I put a pickup coil and connected it to an oscilloscope. Both devices were set to be used with the NXP NFC Cockpit (thus a total of 2 Cockpits were running on my PC). Hereby the CLRC663 was used as a reader and the PN7462 was used as a HCE device. Using the PN7462-NFC Cockpit the ALM mode could be activated and the board did a very strong "simulated" load modulation when communicating with the CLRC663-NFC Cockpit. Below the output of the pickup-coil can be seen:

Moreover, all the ALM settings were accordingly written to the PN7462's EEPROM:

[2023.06.22 17:05:04]:INFO:CardEmulationPN7462ViewModel:Exited Card Mode

[2023.06.22 17:05:04]:INFO:CardEmulationPN7462ViewModel:TX_BITPHASE written with 0x80 for T_TX_A_106_P protocol settings in EEPROM

[2023.06.22 17:05:04]:INFO:CardEmulationPN7462ViewModel:TX_ASKMODE_SELECT written with 0x1 for T_TX_GTM protocol settings in EEPROM

[2023.06.22 17:05:04]:INFO:CardEmulationPN7462ViewModel:TX_CW_AMPLITUDE_ALM_CM written with 0x0 for T_TX_GTM protocol settings in EEPROM

[2023.06.22 17:05:04]:INFO:CardEmulationPN7462ViewModel:TX_PD_CLK_GEN written with 0x1 for T_TX_GTM protocol settings in EEPROM

[2023.06.22 17:05:04]:INFO:CardEmulationPN7462ViewModel:TX_ALM_TYPE_SELECT written with 0x1 for T_TX_GTM protocol settings in EEPROM

[2023.06.22 17:05:04]:INFO:CardEmulationPN7462ViewModel:TX_ALM_ENABLE written with 0x1 for T_TX_GTM protocol settings in EEPROM

[2023.06.22 17:05:04]:INFO:CardEmulationPN7462ViewModel:CLOCK_TX_SEL_SLALM written with 0x0 for T_TX_GTM protocol settings in EEPROM

[2023.06.22 17:05:04]:INFO:CardEmulationPN7462ViewModel:CLOCK_ADC_SEL_RF written with 0x1 for T_TX_GTM protocol settings in EEPROM

[2023.06.22 17:05:04]:INFO:CardEmulationPN7462ViewModel:Entered Card Mode

So far, so good.

I expected that the PN7462 could now be flashed with a sample project, e.g., PN7462AU_ex_phExRf_mcux with only the CM active. Please note that exactly this PN7462 was previously configured to ALM mode using the Cockpit whereas the EEPROM contents was not altered.

While debugging the PN7462 I can see the firmware run to the wStatus = phhalRf_AutoColl(... line in phExRf_CM.c. Accoding to UM10913 Chap 4.10.4 "The AutoColl function takes care of configuring the base rates for all the supported technologies.", so no need to do an Load-Protocol. However, there is no visible ALM on the oscilloscope. Also, when I read the CLIF_TX_CONTROL_REG one line after the phhalRf_AutoColl command it is 0x00, i.e., the TX_ALM_ENABLE bit is 0.

When I flash the Cockpit FW to the PN7462 and start the Cockpit, all ALM settings can be restored and the "Start Cardmode" button also restores the ALM mode.

So the question arises:

- Why does the phhalRf_AutoColl tunction does not activete ALM while the NFC cockpit does? The EEPROM contents was not altered inbetween

- The wMode of phhalRf_AutoColl is set to E_LISTEN_ALL. Would be a pure ALM application be E_LISTEN_ACT_A?

- There are two protocols for HCE according the Cockpit: T_TX_GTM and T_TX_ACT. Where is the difference and which is the important one for phhalRf_AutoColl and the latter CM_106 mode?

Thank you for your help and best regards,

Johannes

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

after further investigation I found out that phhalRf_AutoColl(..) seems to set the register CLIF_ANA_TEST_REG to a value of 0x0150004A. When I set it back to it's reset value 0x50004A using a debugger, phhalRf_AutoColl(..) terminates. Also the ALM starts working then and I can see a strong ISO14443A-106 load modulation.

So what is this 24'th bit that seems to block communication? Is it a good idea to set CLIF_ANA_TEST_REG to it's reset value, e.g., after phhalRf_AutoColl(..) was started?