- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello guys,

Currently I have been struggled with a strange issue: I have configured a SPI master in DSPI_0/SPI_0, however whenever the SPI master send the data, data is duplicated in two first bytes (e.g. 0x1, 0x1, 0x3, 0x3, 0x5, 0x6 instead of 0x1, 0x2, 0x3, 0x4, 0x5, 0x6). All the DSPI settings seems to be correct, and I have gone through all the MC_CGM settings, they are looked good however I realized the FS80 clock frequency is the issue, as I can see the issue is gone when FS80 is increased from 20MHz to 40MHz, although FS80 is not related to DSPI clock source.

Is there any reasonable explanation for this case? Here is my clock tree:

System Clock using PLL source, at 160MHz. PLL chooses XOSC as clock input.

MC_CGM settings:

MC_CGM_SC_DC0[DIV] = 0: S160 = 160Mhz

MC_CGM_SC_DC1[DIV] = 1: S80 = 80Mhz

MC_CGM_SC_DC2[DIV] = 3: S40 = 40Mhz

MC_CGM_SC_DC3[DIV] = 3: F40 = 40Mhz

MC_CGM_SC_DC4[DIV] = 1: F80 = 80Mhz

MC_CGM_SC_DC5[DIV] = 7: FS80 = 20Mhz (increased to 40Mhz in order to get rid of the issue)

MC_CGM_SC_DC6[DIV] = 7: F20 = 20MHz

Best Regards,

Nam

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

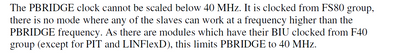

most probably this is due to PBRIDGE that is clocked at FS80, also other modules is running at that clock like DMA, INTC...

RM states that FS80 cannot be lower that 40MHz.

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

most probably this is due to PBRIDGE that is clocked at FS80, also other modules is running at that clock like DMA, INTC...

RM states that FS80 cannot be lower that 40MHz.

BR, Petr