- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- MPC5746CRM: Regarding GPIO configuration

MPC5746CRM: Regarding GPIO configuration

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MPC5746CRM: Regarding GPIO configuration

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello All,

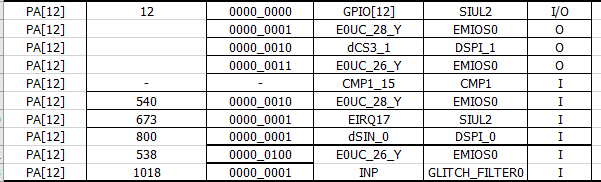

I'm trying to configure a pin PA[12] to be used as an external interrupt.

according to the IO signal description

So I shall configure the MCSR register number 12 first to define it as input, and then go to MCRI register to set the SSS bits.

Considering that the external interrupt is Active low, then I configured the pin to have a pull up and to fire the interrupt on the falling edge.

I forced the interrupt source to be active low for a long time to check that I will get this interrupt many times.

Where I was expecting that the first time the interrupt source with pull the pad level to low then the interrupt will fired for the first time and by clearing the interrupt flag the level of the pad will go back again and then the interrupt source will pull it again to low and then i will get the second interrupt and so on

But actually I got the interrupt only once.

My questions are:

1 - Is my imagination correct that the pad level will be pulled again after the interrupt flag is cleared within the ISR ?

2 - How can I check the pad level either before drive the interrupt or after as I tried to track the GPDI16-19 considering I'm working on EIRQ17 = PA[12] but I found that it is not relevant?

3 - As another approach, Can I configure the pin as GPIO instead of conntecting it to SIUL, considering that I just waiting a pulse on the pin and no need for the SIUL module, am I correct ?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

EIRQ pins are edge sensitive not level sensitive. The user controls the active IRQ edge through the registers SIUL2_IREER and SIUL2_IFEER. When the enabled edge is detected on pin, the corresponding interrupt flag is set in the SIUL2_ISR0 register. This flag is cleared by writing 1 to it. Clearing this flag have no effect on the pad level, this is determined by external signal, if pin is not driven the internal pull up/down determine inactive level.

Pad level is read using SIUL2_GPDIn register if the IBE bit is set.

BR, Petr