- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- QorIQ处理平台

- :

- Layerscape

- :

- Re: QorIQ LS1043A Lowering the CORE frequency from 1.6 GHz to 1.2 GHz

QorIQ LS1043A Lowering the CORE frequency from 1.6 GHz to 1.2 GHz

Hello everyone.

I have been trying to perform this task for several days.

Here is what I am doing:

Target:

My goal is to get my QorIQ LS1043A board (multicore processor) to boot by SD and starting the core to run at 1.2GHz instead of 1.6GHz.

By default all four core of processor works at 1.6GHz. Once the system is up and running, i would like to see from U-boot that all core recive a frequency of 1.2GHz. Sometingh like this:

CPU0(A53):1200 MHz CPU1(A53):1200 MHz CPU2(A53):1200 MHz

CPU3(A53):1200 MHz

Question:

How do I lower the core frequency? portals from 1.6GHz to 1.2GHz?

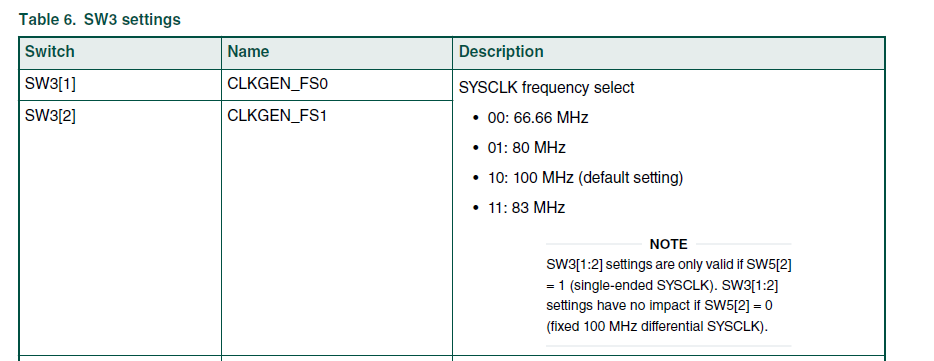

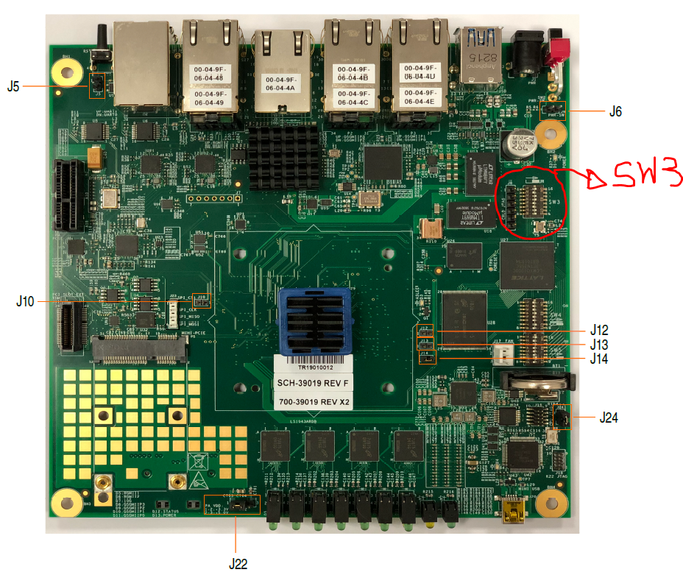

I know that in QorIQ LS1043A there is switch 3 (SW3) which allows you to select the platform clock. This alone is not enough. It is also necessary to configure the RCW register in such a way as to obtain the desired working frequency from us. Looking in the document QorIQ LS1043A Reference Manual, Rev. 6, 07/2020 It is noted that there is a special field called PLL configuration (fields 0-127) for the frequency of the system (frequency of the various COREs) inside RCW.

How should these parameters be set?

On the basis of what reasoning should these parameters of the RCW field be chosen in this way?For instance:

My default board starts with a core frequency of 1.6GHz, and 100MHz of SYSCLK. Going to read the field concerning the frequency of the RCW it turns out that:

- SYS_PLL_CFG: 00; For all valid Platform PLL frequencies. Ok, it's understandable

- SYS_PLL_RAT: 0_0100; This field selects the platform clock:SYSCLK ratio. Why was a 4: 1 ratio chosen?

- MEM_PLL_CFG: 00; All valid DDR PLL frequencies.Ok, it's understandable

- MEM_PLL_RATG: 01_0000, 16:1 ratio. Ok, it's understandable (DDR frequency 1600MT/s ?)

- CGA_PLL1_CFG:00; For Cluster PLL frequencies >= 1 GHz.Ok, it's understandable

- CGA_PLL1_RAT: 01_0000; What is this field for?

- CGA_PLL2_CFG: 00; For Cluster PLL frequencies >= 1 GHz. Ok, it's understandable

- CGA_PLL2_RAT: 001010; 10:1 Async. What is this field for?

- C1_PLL_SEL: 0000; CGA_PLL1/1. What is this field for?

Thanks in advance

已解决! 转到解答。

>SYS_PLL_RAT: 0_0100; This field selects the platform clock:SYSCLK ratio. Why was a 4: 1 ratio chosen?

If you mean the hard coded RCW then answer is “hard coded RCW can be used for correct RCW programming even if 100 MHz SYSCLK is used”.

> CGA_PLL1_RAT: 01_0000; What is this field for?

>C1_PLL_SEL: 0000; CGA_PLL1/1. What is this field for?

The LS1043A four cores are in cluster 1 and run at the same frequency. There are 2 PLLs - CGA PLL1 CGA PLL2 and each this PLL has additional dividers. As result we get 4 possible clock sources for the cluster. C1_PLL_SEL selects which of these clock sources applied to the cluster 1. CGA_PLL1_RAT and CGA_PLL2_RAT define PLL1 and PLL2 output frequencies. Notice these PLLs + dividers also provide clocks for the FMAN & eSDHC and QuadSPI.

>SYS_PLL_RAT: 0_0100; This field selects the platform clock:SYSCLK ratio. Why was a 4: 1 ratio chosen?

If you mean the hard coded RCW then answer is “hard coded RCW can be used for correct RCW programming even if 100 MHz SYSCLK is used”.

> CGA_PLL1_RAT: 01_0000; What is this field for?

>C1_PLL_SEL: 0000; CGA_PLL1/1. What is this field for?

The LS1043A four cores are in cluster 1 and run at the same frequency. There are 2 PLLs - CGA PLL1 CGA PLL2 and each this PLL has additional dividers. As result we get 4 possible clock sources for the cluster. C1_PLL_SEL selects which of these clock sources applied to the cluster 1. CGA_PLL1_RAT and CGA_PLL2_RAT define PLL1 and PLL2 output frequencies. Notice these PLLs + dividers also provide clocks for the FMAN & eSDHC and QuadSPI.