- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

-

- Home

- :

- QorIQ Processing Platforms

- :

- Layerscape

- :

- Re: LS1021A gianfar support

LS1021A gianfar support

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am porting barebox to the LS1021A on a ls1021A-iot. The boot loader boots from SPI and I am now trying to get the gianfar to work. I started port from LSDK-21.08 however the U-boot release on my eval board is U-Boot 2015.01+ls1+g3281947 (Aug 31 2015 - 15:06:00).

I am trying to find the source for -Boot 2015.01 commit 3281947 listed above. It is not found in git://source.codeaurora.org/external/qoriq/qoriq-components/u-boot

At present, the PHY links but nothing is transmitted.

I noticed that in the 2015 version the TX descriptor are read as little endian (#define SCFG_ETSECDMAMCR_LE_BD_FR 0xf8001a0f)

while it seems the 2021 version wants then as big Endian :

board/freescale/ls1021aiot/ls1021aiot.c: clrbits_be32(&scfg->etsecdmamcr, SCFG_ETSECDMAMCR_LE_BD_FR);

#define SCFG_ETSECDMAMCR_LE_BD_FR 0x00000c00

Once I set the bit to big endian then transmit starts to occur according to the driver.

TX status before status = 0x9c00

TX status after status = 0x1c00

Still I see nothing coming out the port. It does not receive either.

The ETSEC2 seems to be programmed correctly as well as the PHY. What else is in the path that could prevent transmission (SMMU, snoop bit). Could be the RCW below:

#disable IFC, enable QSPI and DSPI

0608000a 00000000 00000000 00000000

70000000 00007900 e0025a00 21046000

00000000 00000000 00000000 00038000

20024800 881b7340 00000000 00000000

In the

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Disabling 1000FD/HD advertisement allows packet to go thru. Stopping the investigation here as this is all I need.

Using barebox, I had to increase the receive packet too to avoid a crash.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Disabling 1000FD/HD advertisement allows packet to go thru. Stopping the investigation here as this is all I need.

Using barebox, I had to increase the receive packet too to avoid a crash.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I found why I could not get the port to autonegotiate to 1000FD. This is because the device tree pointed to the wrong TBI for my eTSEC2. Now speed is all good on both my boot loader and Linux.

However, Linux fails to transmit. ping rarely works and I do see lots of TX FIFO errors.

The both Atheros PHY and TBI PHY sow a link up and smartEEE is disabled.

Not sure PHY TX would fail with link up.

Any clue?

I am using Linu x5.11 with an upgraded atheros PHY driver.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

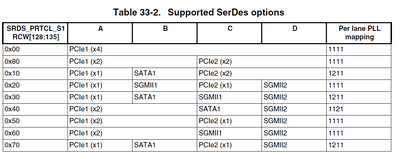

Please refer to the following SerDes configuration on LS1021A platform. In your RCW configuration, you configured RCW[128:135] as 0x70, so SGMII1 on your platform is disabled.

In addition, LSDK 21.08 doesn't support LS1021AIOT, the real-time edge software(https://www.nxp.com/design/software/development-software/real-time-edge-software:REALTIME-EDGE-SOFTW...) supports LS1021AIOT, I extracted u-boot source code from the real-time edge software build environment and uploaded u-boot source code to the following link, please check whether this version u-boot(2020.04) can work on your LS1021AIOT platform.

https://drive.google.com/file/d/1dx0PJ4D8-EuHLFfJoooCk7mdxCk8A1Om/view?usp=sharing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Use the value 0x20 in my boot loader. Now the serdes register are set as U-boot but even though the TX counter increases, nothing go through. I suspect the PHY now as some register are not set the same. Though the speed is correct.

I built U-boot from the git repo you gave me and it does not ping either. The way I have done it is build ls1021aiot_sdcard_defconfig and load it at address 0x82000000. Then go (command)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I built a version of U-boot that does negotiate and ping properly

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Clearly a PHY programming issue. At first I get 1000FD but forcing to autonegotiate give 10HD and pings works.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The other things that is confusing is that U-boot prime Ethernet port is eTSEC2 (it pings) However, the start guide for the ls1021a-iot describes only the port below

ETH0 : SGMII Ethernet eTSEC1

ETH1: SGMII Ethernet eTESC3