- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ

- :

- Re: LPC55S69 (OKDO-E1 Board) SPI first CLK cycle twice long

LPC55S69 (OKDO-E1 Board) SPI first CLK cycle twice long

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

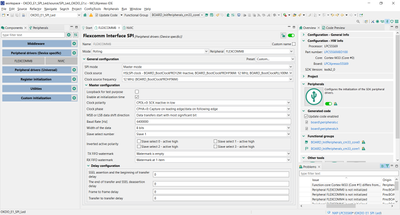

Hi, trying to understand SPI on LPC55s69

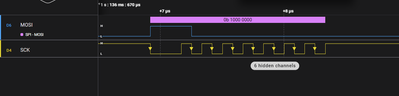

Sent (0b10000000) over SPI MOSI to understand how it work, find out that first CLK cycle duty is twice as long as other.

Can anybody explain to my why and how can I fix that?

(Need identical time cycle to control addressed led)

#include <stdio.h>

#include "board.h"

#include "peripherals.h"

#include "pin_mux.h"

#include "clock_config.h"

#include "LPC55S69_cm33_core0.h"

#include "fsl_debug_console.h"

#define TRANSFER_SIZE (1) /*! Transfer dataSize */

uint8_t masterRxData[TRANSFER_SIZE] = {0};

uint8_t masterTxData[TRANSFER_SIZE] = {0};

int main(void)

{

spi_transfer_t masterXfer;

/* Init board hardware. */

BOARD_InitBootPins();

BOARD_InitBootClocks();

BOARD_InitBootPeripherals();

#ifndef BOARD_INIT_DEBUG_CONSOLE_PERIPHERAL

/* Init FSL debug console. */

BOARD_InitDebugConsole();

#endif

/*Config transfer*/

masterXfer.txData = masterTxData;

masterXfer.rxData = masterRxData;

masterXfer.dataSize = sizeof(masterTxData);

//masterXfer.configFlags = kSPI_FrameAssert;

masterXfer.configFlags = 0;

PRINTF("Debug start \r\n");

masterTxData[0] = 0b10000000;

while(1)

{

SPI_MasterTransferBlocking(FLEXCOMM8_PERIPHERAL, &masterXfer);

for(volatile int i=0;i<500000;i++);

}

return 0;

}

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, @maciek21

According to CPOL=0, the idle level is low, and CPHA=0 is rising edge sampling. While your logic analyzer shows falling edge sampling, you should choose the appropriate trigger edge. You can send me the screenshots of all SPI signals, including CLK, CS, MOSI and MISO.

Best regards, Alex

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, @maciek21

For the first picture, it seems that the clock signal is incorrect, could you please show me all the signals of SPI?

How did you set up CPOL and CPHA? The picture is blurry and I can't see it clearly.

Best regards, Alex

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, @maciek21

According to CPOL=0, the idle level is low, and CPHA=0 is rising edge sampling. While your logic analyzer shows falling edge sampling, you should choose the appropriate trigger edge. You can send me the screenshots of all SPI signals, including CLK, CS, MOSI and MISO.

Best regards, Alex

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, first, thanks for your help.

That's suggestion about CPOL and CPHA kind of answer my question and helped me find solution and fix problem.

The IDLE state for MOSI (and all other SPI signals) in this board is HIGH, as it is physically pulled-up to VCC by a resistor.

Due to this information, I should use CPOL = 1 and CPHA = 1 and that's worked.

I believe further investigation MISO, SSEL or SCK won't be necessary because I only need MOSI to control over led.

Have a good day