- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- Re: LPC55S69 : Chip_GetVersion() ?

LPC55S69 : Chip_GetVersion() ?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LPC55S69 : Chip_GetVersion() ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi !

I can see automatic pin muxing generate a lot of dependencied from chip version

if (Chip_GetVersion()==1)

{

IOCON->PIO[1][9] = ((IOCON->PIO[1][9] &

/* Mask bits to zero which are setting */

(~(IOCON_PIO_FUNC_MASK | IOCON_PIO_DIGIMODE_MASK)))

/* Selects pin function.

* : PORT19 (pin 10) is configured as PIO1_9. */

| IOCON_PIO_FUNC(PIO1_9_FUNC_ALT0)

/* Select Digital mode.

* : Enable Digital mode.

* Digital input is enabled. */

| IOCON_PIO_DIGIMODE(PIO1_9_DIGIMODE_DIGITAL));

}

else

{

IOCON->PIO[1][9] = ((IOCON->PIO[1][9] &

/* Mask bits to zero which are setting */

(~(IOCON_PIO_FUNC_MASK | IOCON_PIO_DIGIMODE_MASK)))

/* Selects pin function.

* : PORT19 (pin 10) is configured as PIO1_9. */

| IOCON_PIO_FUNC(PIO1_9_FUNC_ALT0)

/* Select Digital mode.

* : Enable Digital mode.

* Digital input is enabled. */

| IOCON_PIO_DIGIMODE(PIO1_9_DIGIMODE_DIGITAL));

}

But code looks exactly the same.

Can ConfigTool be configure for support 1B and up revisions only or just latest one.

It looks as some overhead what is no need any more.

Regards,

Eugene

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Eugene,

I have tried to generate the code to configure the PIO1_9 as GPIO function with PinsConfigureTools on MCUXpresso tools, I get the same code.

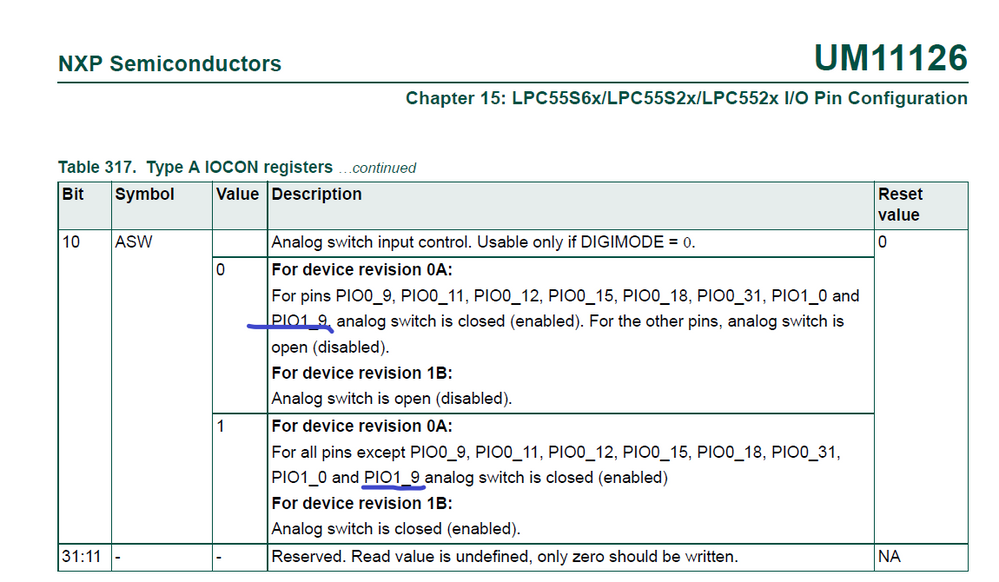

From the Table 317, the AWS bit is valid only when the pin is configured as analog mode by clearing the DIGIMODE bit in IOCON register.

I think the code are the same no matter whether the revision is, the pin configuration is nothing to do with chip version when the pin is configured as GPIO mode.

Hope it can help you.

BR

XiangJun Rong

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi xiangjun.rong !

So this is defect in configuration tool or how to set only 1B revision in it for have clean code ?

Regards,

Eugene

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Eugene,

At the timing being, the PinConfiguration Tools is not smart enough to identify the revision of the chip and generate the corresponding code based on chip revision.

BR

XiangJun Rong