- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

I'm developing a new project with an LPC54102 processor.

In my application the LPC54102 is configured as SPI slave device. When the external SPI master processor tries to communicate with the Slave at frequency higher than 1 MHz and without delay beetwen SPI data bytes, the Slave processor reply with duplicate bytes over the SPI bus.

If the Master processor inserts delay beetwen data bytes of about 10 uS the slave replies correctly up to 20 MHz of SPI clk.

My opinion is the Slave processor is not enought fast in order to fill his SPI out buffer.

Could please help me in order to understand?

Thanks in advance

已解决! 转到解答。

Hi,

Yes, the CPOL/CPHA setting is not related to the /CS signal.

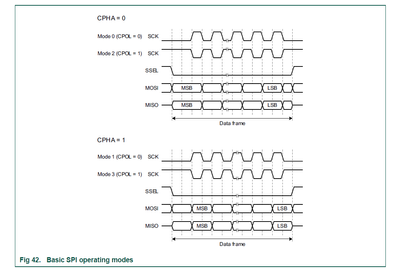

For the CPOL/CPHA setting, the CPOL only controls the polarity of the SCK clock. For the CPHA bit, when the CPHA is 0, the first edge of SCK latches the data, When the CPHA is 1, the second edge of SCK latches the data pin.

I copy it from the section 22.7.1 Operating modes: clock and phase selection from UM10850.pdf.

For your issue that the slave spi transmits duplicate bytes in high sck clock frequency, I agree with you, it is possible that the spi clock is too fast. For the LPC541xx, when the interrupt frequency is more than 1MHz, the core will be overloaded, maybe some of interrupt is missed. I suggest you use SPI FIFO mode, you can write the FIFO with multiple bytes in one ISR, which will save the core load.

BTW, I do not know if you use SDK driver, the SDK driver is inefficient, if you requires maximum transfer rate, I suggest you write the spi register directly without using SDK driver.

Hope it can help you

BR

Xiangjun Rong

Hi, Mirco,

Regarding your question about the SPI clock frequency in slave mode, based on the data sheet of LPC5410x, the maximum supported bit rate for SPI slave mode is 21 Mbit/s.

Regarding your issue "if the Master processor inserts delay between data bytes of about 10 uS the slave replies correctly up to 20 MHz of SPI clk.", do you mean that the /CS has to toggle for each data byte transfer? If it is the case, pls check the CPOL/CPHA configuration and check if the master/salve are the same.

BR

XiangJun Rong

Hi,

Thanks for replay,

Sorry but I'm not understood your second part of replay about CPHA and CPOL.

I know this settings are about clock phase and clock polarity over the SPI interface, are they related also to the CS signal behavior? I think the CS is cleared at the start of SPI transfer and released at the end of transfer independently of CPHA and CPOL configuration do you agree?

Best Regards

Hi,

Yes, the CPOL/CPHA setting is not related to the /CS signal.

For the CPOL/CPHA setting, the CPOL only controls the polarity of the SCK clock. For the CPHA bit, when the CPHA is 0, the first edge of SCK latches the data, When the CPHA is 1, the second edge of SCK latches the data pin.

I copy it from the section 22.7.1 Operating modes: clock and phase selection from UM10850.pdf.

For your issue that the slave spi transmits duplicate bytes in high sck clock frequency, I agree with you, it is possible that the spi clock is too fast. For the LPC541xx, when the interrupt frequency is more than 1MHz, the core will be overloaded, maybe some of interrupt is missed. I suggest you use SPI FIFO mode, you can write the FIFO with multiple bytes in one ISR, which will save the core load.

BTW, I do not know if you use SDK driver, the SDK driver is inefficient, if you requires maximum transfer rate, I suggest you write the spi register directly without using SDK driver.

Hope it can help you

BR

Xiangjun Rong

Hi xiangjun_ron,

Thanks a lot for support, the issue seems to be sloved using Tx and Rx FIFO features over SPI. Now the SPI communication works up to 15 MHz without delay betweern data Bytes.

Best Regards