- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- LPC4370 ADCHS high interrupt jitter

LPC4370 ADCHS high interrupt jitter

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LPC4370 ADCHS high interrupt jitter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello.

Our application uses HSADC and DMA to write samples to RAM. We also use threshold crossing interrupt to search signal edges.

We achieved the minimum HSADC ISR calling delay by moving the interrupt table and handler to RAM. Now it is about 100 ns. However, this value can only be obtained if the microcontroller is in interrupt wait mode (__WFI()) before it is triggered. If the microcontroller performs any functions before the interrupt is triggered, the delay time becomes unstable and can take values from 100 ns to 2 μs.

Using code optimization and transferring all software to RAM improves stability a little, but does not completely solve the problem. Tell us, please, how to get around this problem?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Vitaliy,

You are right, for the MPU, if you configure region incorrectly, when you access the region, the MemManage exception will be triggered. If you don’t have an exception; accordingly, the region has the correct configuration.

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi. xiangjun.rong

That is, at the moment, the cause of the problem is unclear?

I noticed that MPU allows you to disable caching for different regions. Perhaps this can speed up the code and reduce jitter time of ISR call?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Vitaliy,

I think your problem becomes the question how the LPC4370 can run in parallel, for example when the ADC interrupt happens, all the processes occur simultaneously. The DMA transfer data from ADC result register to memory, while the core fetches code from spifi flash or onm-chip RAM, the core writes registers to stack, so it is difficult.

Anyway, pls refer to the Fig 2. LPC4370 Block diagram (flashless parts, triple-core, 12-bit ADCHS) in UM10503.pdf, put the code into on-chip RAM and run in on-chip, while keep in mind that you have to use different bus so that all the process can run in parallel.

I do not know if it can help you.

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, xiangjun.rong

Thanks for your answer. We tried to transfer all the code to RAM, and with this we turned off the parallel operation of DMA. Problems begin to occur as soon as the CPU performs any functions during the occurrence of an interrupt. And the more complex and voluminous the function, the greater the delay of the interrupt handler.

We thought that perhaps the CPU is caching the current instructions, and this takes time.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Vitaliy,

As you know that the LPC4370 has MPU(Memory Protection Unit), you have to configure the SRAM as a region so that the SRAM location is code-fetch enabled.

Pls refer to the following section.

I copy the UM of Cortex-M4, which includes the MPU chapter.

Hope it can help you

BR

Xiangjun Rong

3.3.6 Memory Protection Unit (MPU)

The MPU is a integral part of the ARM Cortex-M4 for memory protection and supported by

all LPC43xx parts. The processor supports the standard ARMv7 Protected Memory

System Architecture model. The MPU provides full support for:

• protection regions

• overlapping protection regions, with ascending region priority (7 = highest priority, 0 =

lowest priority)

• access permissions

• exporting memory attributes to the system

MPU mismatches and permission violations invoke the programmable-priority

MemManage fault handler. See the ARMv7-M Architecture Reference Manual for more

information.

The access permission bits, TEX, C, B, AP, and XN, of the Region Access Control

Register control access to the corresponding memory region. If an access is made to an

area of memory without the required permissions, a permission fault is raised. For more

information, see the ARMv7-M Architecture Reference Manual.

The MPU is used to enforce privilege rules, to separate processes, and to enforce access

rules. For details on how to use the MPU and for the register description refer to the ARM

Cortex-M4 Technical Reference Manual.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, xiangjun.rong

Thanks for your answer.

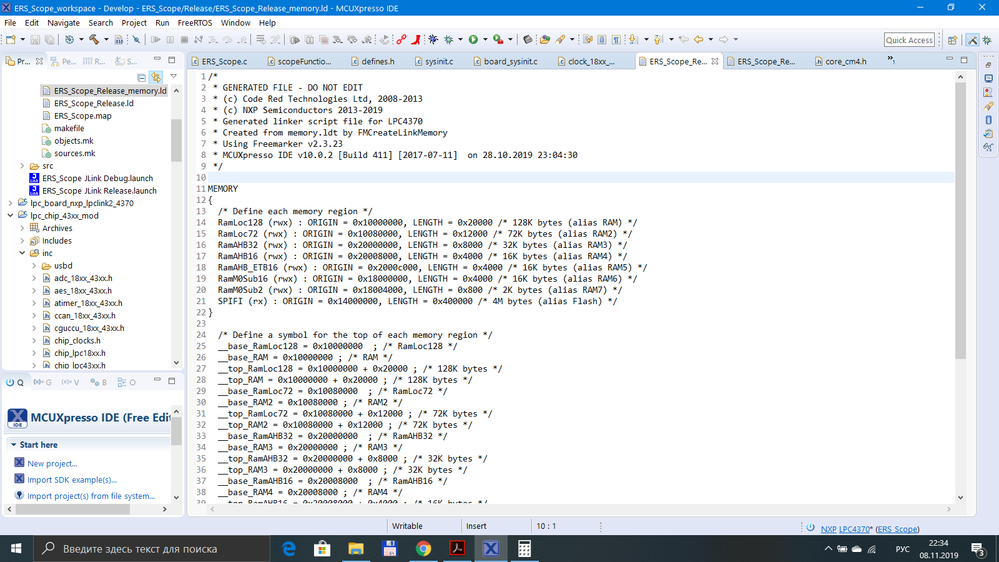

We have the following configuration of regions.

The code is executed from the RamLoc128 region. If I correctly understood the purpose of the MPU, it throws an exception if we try to execute code from a region that is not intended for this. We don’t have an exception; accordingly, our region has the correct configuration, right? Please correct me if I misunderstood you.