- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ

- :

- LPC1817 EMC Interface read cycle

LPC1817 EMC Interface read cycle

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

LPC1817 EMC Interface read cycle

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi NXP support team,

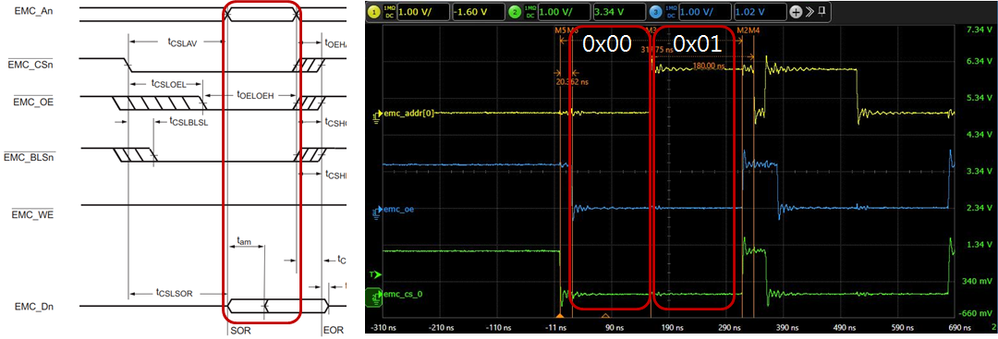

I got an issue about LPC1817 EMC interface read cycle. I connected the EMC(Static memory) interface to SRAM in my design. When I issued one read cycle, I got two EMC address(0x00 -> 0x01) toggle from scope as follows. It made the read data error. It should be one address in one read cycle. My EMC configuration as follows. Do you have any ideas? Thanks.

//======================================EMC Configuration===================================

LPC_EMC->STATICCONFIG0 = ( (0 << 0) | // Memory width 8-bit

(0 << 3) | // Async page mode disable

(0 << 6) | // Active LOW chip select

(1 << 7) | // Byte lane state: use WE signal

(0 << 19) ); // Disable buffer

LPC_EMC->STATICWAITWEN0 = 0x2; // Wait output enable: 2 delay

LPC_EMC->STATICWAITOEN0 = 0x2; // Wait output enable: 2 delay

LPC_EMC->STATICWAITTURN0 = 0x0;

LPC_EMC->STATICWAITPAG0 = 0x0;

LPC_EMC->STATICWAITWR0 = 0x0F;

LPC_EMC->STATICWAITRD0 = 0x0F;

LPC_EMC->CONTROL = ( (1 << 0) | //EMC Enable

(0 << 1) ); //EMC Addr non-mirror

emc

lpc18xx

lpc1817

lpc18xx lpcopen

external memery

external ram

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Chase,

Hope you are doing well. It is possible that an EMC will perform a burst read access even when the buffer enable bit is disabled. In the case of the configurations you have provided the bit 19 of the Static Memory Configuration register that is described in table 369 of the user manual.

Burst read means that if you were meant to read register 0(even with the buffer disabled) it will read 0 and 1.

Let me know if you have further questions.

Best Regards,

Sabina

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Bruce,

So I couldn't use any methods to disable the burst read ? Thanks.