- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ

- :

- Re: LPC11U68 Synchronous Mode USART0

LPC11U68 Synchronous Mode USART0

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

LPC11U68 Synchronous Mode USART0

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I'm having a weird problem with using the synchronous mode on the USART0 peripheral.

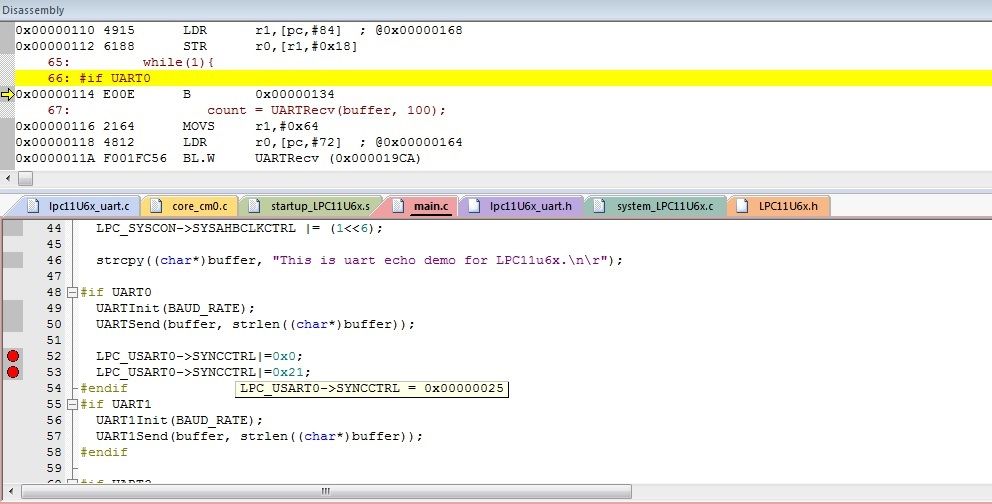

I need to receive a bit stream sampled on the rising edge of a clock with no end or start bits, but attempting to set both of these parameters sets the sampling bit to falling. I can do rising with end and start or falling and no end and start but not both rising and no end and start. I can't even change it using the memory inspector in LPCXpresso.

For clarity, the syncctrl register goes to 0x25 when I try to set it to 0x21.

This is the exact configuration I'm using

Chip_UART0_Init(LPC_USART0);

Chip_Clock_EnablePeriphClock(SYSCTL_CLOCK_UART0);

LPC_USART0->SYNCCTRL|=UART0_SYNCCTRL_SYNC|UART0_SYNCCTRL_STARTSTOPDISABLE; // Enable sync mode

Chip_UART0_SetupFIFOS(LPC_USART0,UART0_FCR_FIFO_EN); //Enable Input FIFO

Chip_IOCON_PinMuxSet(LPC_IOCON, 0, 17,(IOCON_FUNC3 | IOCON_MODE_INACT));

Chip_IOCON_PinMuxSet(LPC_IOCON, 0, 18,(IOCON_FUNC1 | IOCON_MODE_INACT));

How do I get around this issue, or is this some weird limitation of the chip?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

UM mentioned:

Data changes on TxD from falling edges on SCLK. When SSDIS is 0, the FES bit controls

whether the USART0 samples serial data on RxD on rising edges or falling edges on

SCLK. When SSDIS is 1, the USART0 ignores FES and always samples RxD on falling

edges on SCLK.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

This doesn't fix my problem. The code you sent has the same problem.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

According to the policy, can you let us know your company and the project you're working on now?

Thanks for your understanding.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Nicholas Hunn,

Thanks for your reply.

I've also replicated the issue, and I will contact with AE team for checking.