- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ

- :

- Re: LPC 824 detailed function of DMA

LPC 824 detailed function of DMA

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

LPC 824 detailed function of DMA

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I am using DMA to transfer data to and from USART in a LPC824. The transfer length will vary.

When receiving data, I have programmed DMA transfer to fill a buffer but I want to process data even if the buffer is not full. If I stop a DMA channel with ENABLECLR registers, could there be one byte that is read from the USART by DMA but not yet written to the buffer?

When sending data, I would sometimes like to send more data when a DMA transfer is already running.

Is it possible to stop the DMA channel with ENABLECLR register, modify the channel descriptor (increase count and ending address) and then start the channel again with ENABLESET? Or is it then a risk to lose data?

There is a picture (Fig. 19) in the User Manual where there are some rectangles marked source/destination address fetch, address cache, source/destination data. It would be helpful to know more exactly how DMA works. Is there only one read of channel descriptor at start of a transfer? What is cached? If there is a 8-bit or 16-bit transfer, will there be one read/write of RAM for each transfer or will it be 32-bit transfers to RAM? Will both read and write for one transfer always be done or is it possible to halt DMA between read and write operation?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

The DMA interrupt will only come after the current transfer is complete, so it is not of any use. My problem is that I want to process incoming data already when some data has arrived, but I don't want to lose any data. The User manual could be much clearer.

According to the manual, when you disable a channel, there can still be some activity as long as the channel's BUSY bit is on. If I at the point when BUSY is 0 change XFERCNT in the XFERCFG register and source or destination end address in the channel descriptor, is it then safe to enable the channel with new parameters or should I abort the operation using the ABORT register and then start a new DMA operation?

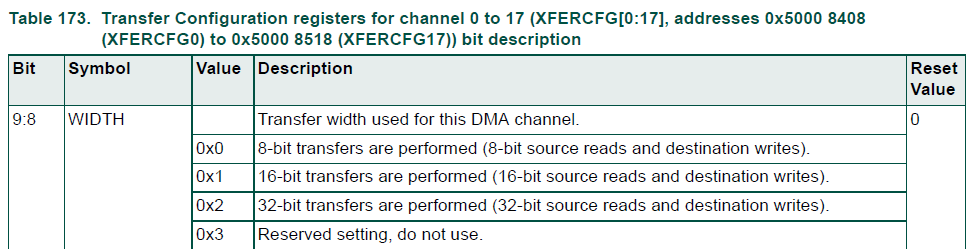

My question about transfer width was not how you do it. I am fully aware of that. A highly intelligent DMA controller could first read 4 bytes from a peripheral and then write the data to RAM as one 32-bit word. The rectangles in Fig 19 with source and destination data suggests that it might be so. But it is much simpler to just perform a byte read/write to RAM. If this is the case, it would make sense to have buffers that are multiple of words.

There is also an error interrupt register in the DMA controller, but absolutely no information what that causes a DMA error. It would be interesting to know.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Kurt,

I'm facing exactly the same issue : I want to read data from the buffer before switching to the next ping pong buffer. Have you been able to make it work?

If so, could you please share the algorithm?

thanks !

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Victor,

If you only want to read data in buffer, I think it is safe to just read XFERCNT in the XFERCFG register to follow how far the DMA transfer has gone. If you want to fiddle with DMA parameters, you should disable the channel, wait for not busy, change parameters and enable the channel again.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Kurt,

Thanks for your answer.

[EDIT] it works :smileyhappy:

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I am uncertain if your separate email was before or after the comment above.

I suggest that you first get ping-pong DMA transfer working so that it actually works with two buffers.

It is not necessary to abort DMA transfer. You can just read XFERCNT in the XFERCFG and process

all data in buffer up to that point even if DMA continues to run in that buffer. I have not checked the exact order when XFERCNT is updated and when data is stored in memory, but even if data is stored after, there will be number of clock cycles from reading XFERCFG to reading data in DMA buffer.

In user manual, there is a statement in Table 173 that as usual is not completely clear:

XFERCOUNT

Total number of transfers to be performed, minus 1 encoded. The number of bytes

transferred is: (XFERCOUNT + 1) x data width (as defined by the WIDTH field).

Remark: The DMA controller uses this bit field during transfer to count down.

Hence, it cannot be used by software to read back the size of the transfer, for

instance, in an interrupt handler.

This bitfield is counting down during transfer. It would have been clearer if the statement was that it can be read to determine how much is transferred and also if transfer is complete when this bitfield has decremented.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Kurt,

About the DMA error interrupt, because the cause will be many kind according detail application, it's impossible checked and listed. Only can provide the result.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Kurt Mirdell ,

" If I stop a DMA channel with ENABLECLR registers, could there be one byte that is read from the USART by DMA but not yet written to the buffer?"

-> I don't think so, because the DMA transfer is very fast. While to be on the safe side, you can pause it in DMA interrupt.

"If there is a 8-bit or 16-bit transfer, will there be one read/write of RAM for each transfer or will it be 32-bit transfers to RAM?"

-> You can config the transfer width:

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------