- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- MCUXpressoソフトウェアとツール

- :

- Kinetisソフトウェア開発キット

- :

- SPI data delay problem

SPI data delay problem

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

SPI data delay problem

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

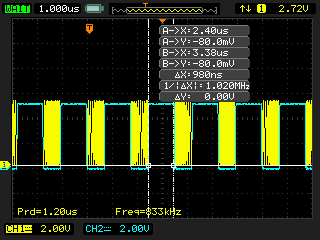

I am using SPI0 (interrupt based) on the KEA128 MCU. I am trying to transmit 4 bytes of data in buffer to the slave device using SPI mode 0. There are delays between each byte that are being transmitted. The attached image shows my SPI transmission captured using a Digital Oscilloscope; I have captured only the SlaveSelect and Clock waveforms. The MCU is running at 48 MHz with SPI of 12 MHz. I used KEAZ128 SDK for SPI.

Initialization:

SIM_PINSEL0 |= SIM_SCGC_SPI0_MASK;

SPI_ConfigType sSPIConfig = {{0}};

sSPIConfig.u32BitRate = 12000000;

sSPIConfig.u32BusClkHz = 24000000;

sSPIConfig.sSettings.bModuleEn = 1;

sSPIConfig.sSettings.bMasterMode = 1;

sSPIConfig.sSettings.bClkPhase1 = 0;

sSPIConfig.sSettings.bClkPolarityLow = 0;

sSPIConfig.sSettings.bMasterAutoDriveSS = 1;

sSPIConfig.sSettings.bTxIntEn = 1;

sSPIConfig.sSettings.bIntEn = 1;

SPI_SetCallback(SPI0,SPI0_ISR);

SPI_Init(SPI0, &sSPIConfig);

ISR:

volatile uint8_t index = 0;

void SPI0_ISR()

{

(void)SPI0_S;

if ((SPI0_S & SPI_S_SPTEF_MASK)) // Check Tx buffer staus flag@@@ is empty

{

if( index == 4)

{

index = 0;

SPI0_C1 &=~ SPI_C1_SPTIE_MASK;

}

else

{

SPI0_D = tx_buffer[index++];

}

}

}

Main:

I initialized SPI then I started the following:

volatile uint8_t tx_buffer[4] = {0};

tx_buffer[0] = 0x12;

tx_buffer[1] = 0x10;

tx_buffer[2] = 0x11;

tx_buffer[3] = 0x15

SPI0_C1 &=~ SPI_C1_SPIE_MASK ; // Disable Receiver

SPI0_C1 |= SPI_C1_SPTIE_MASK ; // Enable only transmitter interrupt

while(1);

The Result of the above program is attached below.The Blue coloured waveform is the SlaveSelect and the Yellow is the SPI Clock Pulses. As you see the SPI for transmitting 32 bit should be (1/(12 Mhz)) * 32 Bit = 3 u-sec(microseconds), but the actual time taken to transmit is 10 u-sec as seen with the Oscilloscope . The maximum observed delay between bytes is 2.3 u-sec. In my program it is processing only SPI Interrupt as I hold the processor (after enabling interrupt). I am not running any timer. Please help me to resolve delay issue between bytes and also overall time.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Elango M,

Thank you for your testing.

I also test your code today.

Actually, even use this code directly:

void SPI0_ISR (void)

{

(void)SPI0_S;

if ((SPI0_S & SPI_S_SPTEF_MASK)) // Check Tx buffer staus flag@@@ is empty

{

SPI0_D = 0x55;

}

}

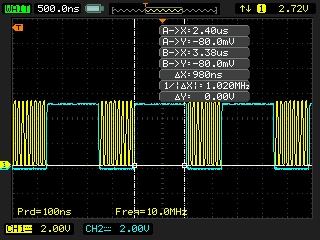

I also can find about 1us delay in the SPI bus!

You can find the intervals is about 1us.

Actually, this is normal, let me tell you the details.

As you know, the system clock is just 48Mhz, but your SPI baudrate is 12Mhz.

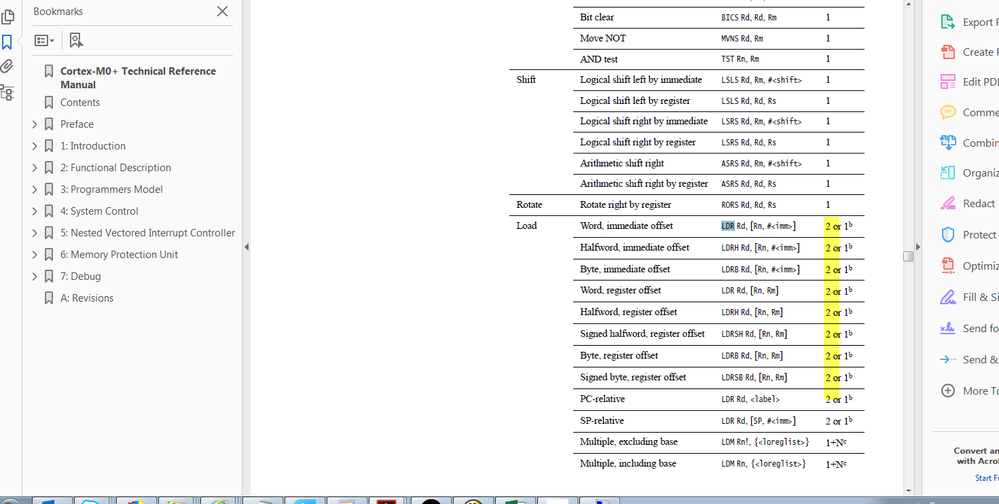

From the ARM CortexM0+ core document, you can know, the Interrupt Latency is 16cycles.

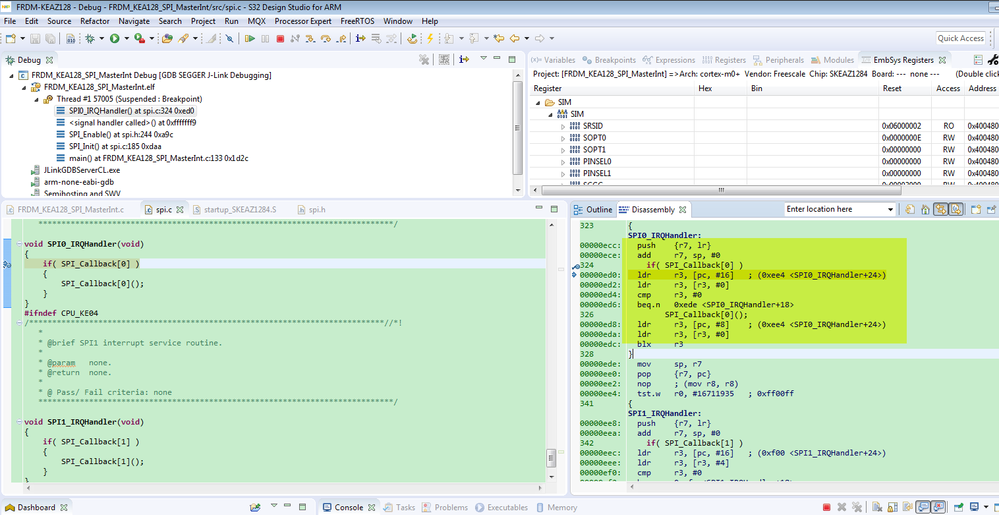

Then debug the code, you can find the ISR asm code:

So, just add the whole ISR asm code execution time, also add your callback time:

As I know, it is about 50 cycles core clock, now ,just take 50cycles as an example.

50*(1/48Mhz)=1.04us.

This is the root reason why you have this gap between the SPI bytes, it is caused by the system clock can't too be high, and your SPI baudrate is very high.

So, if you don't want to have the gap, you can minimize the SPI baudrate, or delete the callback, just add the code in SPI0_IRQHandler, but this also have gap, just cut down.

As I know, 1Mhz won't have the gap.

Wish it helps you!

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------