- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Trace versus SDHC on K64

Trace versus SDHC on K64

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Trace versus SDHC on K64

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Looking at the K64 tower board schematic, it has the SDHC card data and clock tied to the JTAG trace data and clock lines. When we spin our own board for this project, we do want to keep the SDHC socket but also want to be able to use the trace capability and will only have the JTAG/trace connector, not the tower board’s separate K20 MCU for the USB debug interface. (The SDHC and trace functions are shared on the same dedicated pins on the MCU, so this is obviously something that Freescale has thought about.)

I’m wondering how well these will coexist with each other and what we will have to do so we can debug and use an SD card without losing the trace capability?

If you have any guidance or can point to application notes or other information, I’d really appreciate the hints.

Thanks!

Mark

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mark Sample,

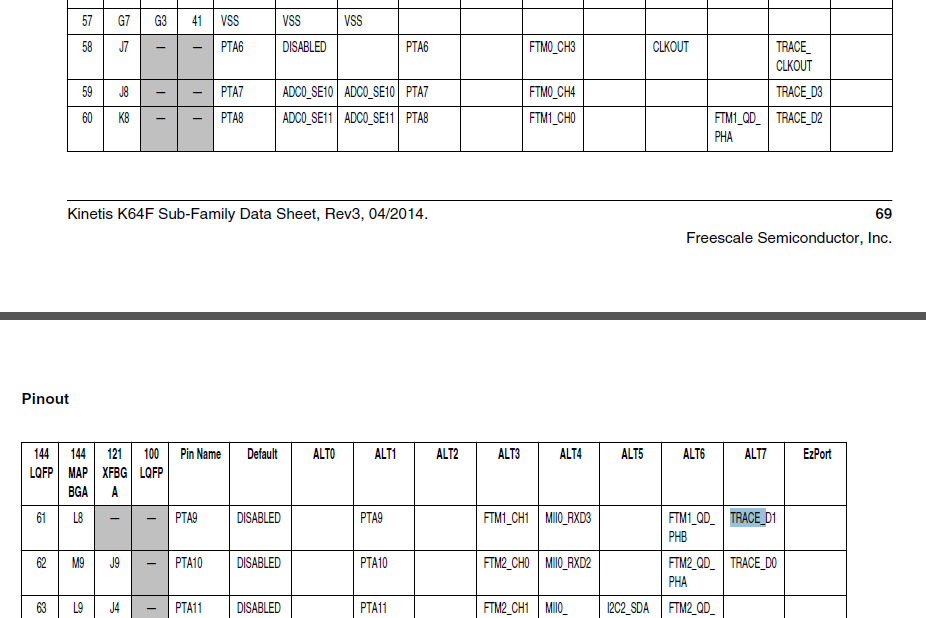

If you refer to the K64 data sheet, you may find alternative pins for trace function on PTA[6..10]. Please refer to the following for details.

Hope that helps

Have a great day,

Kan

Freescale Technical Support

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Mark

The trace pins are MUX functions that the SW much set up (the pins don't default to trace function) and the trace pins are usually available on multiple pins.

For example SDHC0_D0 and TRACE_D3 are both on the port PTE1. This defaults to ADC input and so the software decides whether to use it as SDHC or Trace.

In your case you will probably prefer to use the pin as SDHC_D0 always and so you can instead select TRACE_D3 to be on PTA7 instead, which is an alternate location (and hopefully you won't be using that for one of its other functions).

It will however also be housing dependent as to whether there is a trace connection and how many alternatives the trace pins have - some smaller housings may be less flexible since they simply don't have all pins available.

Therefore if you are now defining the circuitry you may be able to work out the pin utilisation so that you can keep the trace lines aways from the SDHC interface and then have no restrictions.

If this is not possible the software will need to "temporarily" disable SDHC mode in favoir of the trace functionality. Once debugging has completed it can then re-enable the interface.

Regards

Mark

Kinetis: http://www.utasker.com/kinetis.html

K64: http://www.utasker.com/kinetis/FRDM-K64F.html / http://www.utasker.com/kinetis/TWR-K64F120M.html / http://www.utasker.com/kinetis/TWR-K65F180M.html

For the complete "out-of-the-box" Kinetis experience and faster time to market

:smileyinfo: Out-of-the-box support for 46 Kinetis boards and 10 IDEs (460 combinations from a single code source with no porting required)