- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: Proper programming of the eDMA that incorporates int_major and scatter/gather

Proper programming of the eDMA that incorporates int_major and scatter/gather

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Proper programming of the eDMA that incorporates int_major and scatter/gather

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello, I am working with the Freedom K64F, using the eDMA. I am properly able to configure a chain of software TCDs using Scatter/Gather, and they each call the next SGA. Once the major count is completed, I want to trigger an interrupt, perform some processing in the DMA0 ISR, then within the ISR; I want to signal the channel to start on the next TCD that "hopefully" has loaded with the last SGA from the previous SGA.

When I run the debug, the 1st DMA0 ISR gets called, I perform the processing, clear the DMA0 Interrupt in the CR_CINT register and then trigger the channel. However, the ISR appears to be stuck in an ISR of some sort.

!) Am I missing something in my flow?

2) Is the SGA compatible with using int_major/int_half? Do I have to instead push the next software TCD within the ISR?

3) Does clearing the DMA Channel Interrupt with CR_CINT also clear the NVIC or does it automatically clear the NVIC when the CR_INT is cleared?

Thanks!

Duane

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Duane Owens

It's difficult to follow your issue if I don't have your full project to try to find the problem, so could you share your project?

Also, have you check the Doc: https://community.nxp.com/docs/DOC-329546

please give it a try and tell me if it helps.

Best Regards

Jorge Alcala

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Any updates on this Jorge?

Thank you!

Duane

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

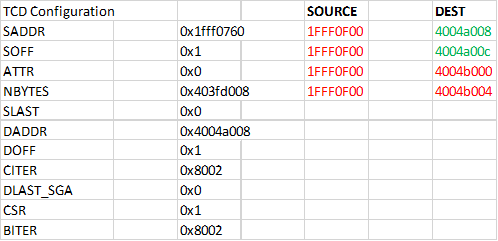

Thanks Jorge, Yes, I have read that document as well as the one on Major/Minor Channel Linking, and continually searched the community. I am having a couple of NCE errors, but I'd like to solve the 1st NCE error first: I am transferring 8 32bit PORT PCR configuration values from memory to the PORT registers. Here's my TCD for the eDMA configuration and the memory addresses:

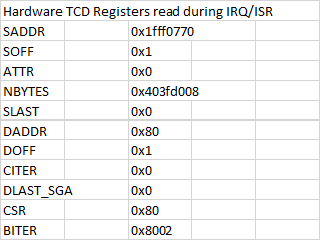

I enabled Interrupts on Error and captured the Hardware TCD state:

The error that triggered the interrupt was an NCE error. The Done flag is set in the CSR and the data has been transferred to the destination registers. But, the NCE error causes other problems when using SGA to the next TCD, I think because the NCE flag is still set, even if I clear the Error Int flag. The VLD bit gets cleared, but the NCE bit stays set.

I can break the transfer up into 2 transfers (between the 4004A00C and 4004B004), but I was still hoping to consolidate the transfer into as few of TDCs as possible. I also tried to set the INTHALF but, it never fired the interrupt... only the INTMAJ works.

I thought I saw one thread that the user couldn't get the Minor Loop Channel Linking to work, but I don't know if that's related.

Thanks for your time.

Duane