- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: MK21 DMA SPI2 problems

MK21 DMA SPI2 problems

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

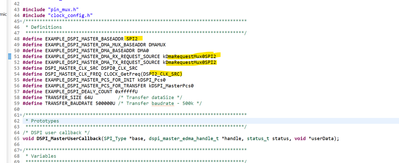

I'm trying to transmit data via SPI2 peripheral, using DMA in my MK21FX512AVMD12. I'm looking at the drivers examples (twrk21f120m_dspi_edma_b2b_transfer_master, twrk21f120m_dspi_half_duplex_edma_master)....and I see diferences when I use SPI2 instead SPI0. In those examples for the SPI0 peripheral the callback is called adequately, but when I change to SPI2, it is not called. These are the changes that I apply:

In the edma_spi driver it is clear that both peripherals are different, because SPI0 has separate DMA request and SPI2 don't.

Do I have to change anything else in order to use SPI2?

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I could not get the twr-k21 but I make some tests with the frdm-k22 this is the code I modified and tested.

/*

* Copyright (c) 2015, Freescale Semiconductor, Inc.

* Copyright 2016-2017 NXP

* All rights reserved.

*

* SPDX-License-Identifier: BSD-3-Clause

*/

#include "fsl_device_registers.h"

#include "fsl_debug_console.h"

#include "fsl_dspi.h"

#include "pin_mux.h"

#include "clock_config.h"

#include "board.h"

#include "fsl_dspi_edma.h"

#include "fsl_edma.h"

#include "fsl_dmamux.h"

/*******************************************************************************

* Definitions

******************************************************************************/

#define EXAMPLE_DSPI_MASTER_BASEADDR SPI1

#define EXAMPLE_DSPI_MASTER_DMA_MUX_BASEADDR DMAMUX

#define EXAMPLE_DSPI_MASTER_DMA_BASEADDR DMA0

#define EXAMPLE_DSPI_MASTER_DMA_TX_RX_REQUEST_SOURCE kDmaRequestMux0SPI1

//#define EXAMPLE_DSPI_MASTER_DMA_TX_REQUEST_SOURCE kDmaRequestMux0SPI0Tx

#define DSPI_MASTER_CLK_SRC DSPI1_CLK_SRC

#define DSPI_MASTER_CLK_FREQ CLOCK_GetFreq(DSPI1_CLK_SRC)

#define EXAMPLE_DSPI_MASTER_PCS_FOR_INIT kDSPI_Pcs0

#define EXAMPLE_DSPI_MASTER_PCS_FOR_TRANSFER kDSPI_MasterPcs0

#define EXAMPLE_DSPI_DEALY_COUNT 0xfffffU

#define TRANSFER_SIZE 64U /* Transfer dataSize */

#define TRANSFER_BAUDRATE 500000U /* Transfer baudrate - 500k */

/*******************************************************************************

* Prototypes

******************************************************************************/

/* DSPI user callback */

void DSPI_MasterUserCallback(SPI_Type *base, dspi_master_edma_handle_t *handle, status_t status, void *userData);

/*******************************************************************************

* Variables

******************************************************************************/

uint8_t masterRxData[TRANSFER_SIZE] = {0};

uint8_t masterTxData[TRANSFER_SIZE] = {0};

dspi_master_edma_handle_t g_dspi_edma_m_handle;

edma_handle_t dspiEdmaMasterRxRegToRxDataHandle;

#if (!(defined(FSL_FEATURE_DSPI_HAS_GASKET) && FSL_FEATURE_DSPI_HAS_GASKET))

edma_handle_t dspiEdmaMasterTxDataToIntermediaryHandle;

#endif

edma_handle_t dspiEdmaMasterIntermediaryToTxRegHandle;

volatile bool isTransferCompleted = false;

volatile uint32_t g_systickCounter = 20U;

/*******************************************************************************

* Code

******************************************************************************/

void SysTick_Handler(void)

{

if (g_systickCounter != 0U)

{

g_systickCounter--;

}

}

void DSPI_MasterUserCallback(SPI_Type *base, dspi_master_edma_handle_t *handle, status_t status, void *userData)

{

if (status == kStatus_Success)

{

PRINTF("This is DSPI master edma transfer completed callback. \r\n\r\n");

}

isTransferCompleted = true;

}

/*!

* @brief Main function

*/

int main(void)

{

BOARD_InitBootPins();

BOARD_InitBootClocks();

BOARD_InitDebugConsole();

PRINTF("DSPI board to board edma example.\r\n");

PRINTF("This example use one board as master and another as slave.\r\n");

PRINTF("Master and slave uses EDMA way. Slave should start first. \r\n");

PRINTF("Please make sure you make the correct line connection. Basically, the connection is: \r\n");

PRINTF("DSPI_master -- DSPI_slave \r\n");

PRINTF(" CLK -- CLK \r\n");

PRINTF(" PCS -- PCS \r\n");

PRINTF(" SOUT -- SIN \r\n");

PRINTF(" SIN -- SOUT \r\n");

PRINTF(" GND -- GND \r\n");

/* DMA Mux setting and EDMA init */

uint32_t masterRxChannel, masterTxChannel;

edma_config_t userConfig;

masterRxChannel = 0U;

masterTxChannel = 1U;

/* If DSPI instances support Gasket feature, only two channels are needed. */

#if (!(defined(FSL_FEATURE_DSPI_HAS_GASKET) && FSL_FEATURE_DSPI_HAS_GASKET))

uint32_t masterIntermediaryChannel;

masterIntermediaryChannel = 2U;

#endif

/* DMA MUX init */

DMAMUX_Init(EXAMPLE_DSPI_MASTER_DMA_MUX_BASEADDR);

DMAMUX_SetSource(EXAMPLE_DSPI_MASTER_DMA_MUX_BASEADDR, masterRxChannel, (uint8_t)EXAMPLE_DSPI_MASTER_DMA_TX_RX_REQUEST_SOURCE);

DMAMUX_EnableChannel(EXAMPLE_DSPI_MASTER_DMA_MUX_BASEADDR, masterRxChannel);

#if (defined EXAMPLE_DSPI_MASTER_DMA_TX_REQUEST_SOURCE)

DMAMUX_SetSource(EXAMPLE_DSPI_MASTER_DMA_MUX_BASEADDR, masterTxChannel, (uint8_t)EXAMPLE_DSPI_MASTER_DMA_TX_REQUEST_SOURCE);

DMAMUX_EnableChannel(EXAMPLE_DSPI_MASTER_DMA_MUX_BASEADDR, masterTxChannel);

#endif

/* EDMA init */

/*

* userConfig.enableRoundRobinArbitration = false;

* userConfig.enableHaltOnError = true;

* userConfig.enableContinuousLinkMode = false;

* userConfig.enableDebugMode = false;

*/

EDMA_GetDefaultConfig(&userConfig);

EDMA_Init(EXAMPLE_DSPI_MASTER_DMA_BASEADDR, &userConfig);

uint32_t srcClock_Hz;

uint32_t errorCount;

uint32_t loopCount = 1U;

uint32_t i;

dspi_master_config_t masterConfig;

dspi_transfer_t masterXfer;

/* Master config */

masterConfig.whichCtar = kDSPI_Ctar0;

masterConfig.ctarConfig.baudRate = TRANSFER_BAUDRATE;

masterConfig.ctarConfig.bitsPerFrame = 8;

masterConfig.ctarConfig.cpol = kDSPI_ClockPolarityActiveHigh;

masterConfig.ctarConfig.cpha = kDSPI_ClockPhaseFirstEdge;

masterConfig.ctarConfig.direction = kDSPI_MsbFirst;

masterConfig.ctarConfig.pcsToSckDelayInNanoSec = 1000000000U / TRANSFER_BAUDRATE;

masterConfig.ctarConfig.lastSckToPcsDelayInNanoSec = 1000000000U / TRANSFER_BAUDRATE;

masterConfig.ctarConfig.betweenTransferDelayInNanoSec = 1000000000U / TRANSFER_BAUDRATE;

masterConfig.whichPcs = EXAMPLE_DSPI_MASTER_PCS_FOR_INIT;

masterConfig.pcsActiveHighOrLow = kDSPI_PcsActiveLow;

masterConfig.enableContinuousSCK = false;

masterConfig.enableRxFifoOverWrite = false;

masterConfig.enableModifiedTimingFormat = false;

masterConfig.samplePoint = kDSPI_SckToSin0Clock;

srcClock_Hz = DSPI_MASTER_CLK_FREQ;

DSPI_MasterInit(EXAMPLE_DSPI_MASTER_BASEADDR, &masterConfig, srcClock_Hz);

/* Set up dspi master */

memset(&(dspiEdmaMasterRxRegToRxDataHandle), 0, sizeof(dspiEdmaMasterRxRegToRxDataHandle));

#if (!(defined(FSL_FEATURE_DSPI_HAS_GASKET) && FSL_FEATURE_DSPI_HAS_GASKET))

memset(&(dspiEdmaMasterTxDataToIntermediaryHandle), 0, sizeof(dspiEdmaMasterTxDataToIntermediaryHandle));

#endif

memset(&(dspiEdmaMasterIntermediaryToTxRegHandle), 0, sizeof(dspiEdmaMasterIntermediaryToTxRegHandle));

EDMA_CreateHandle(&(dspiEdmaMasterRxRegToRxDataHandle), EXAMPLE_DSPI_MASTER_DMA_BASEADDR, masterRxChannel);

#if (!(defined(FSL_FEATURE_DSPI_HAS_GASKET) && FSL_FEATURE_DSPI_HAS_GASKET))

EDMA_CreateHandle(&(dspiEdmaMasterTxDataToIntermediaryHandle), EXAMPLE_DSPI_MASTER_DMA_BASEADDR, masterIntermediaryChannel);

#endif

EDMA_CreateHandle(&(dspiEdmaMasterIntermediaryToTxRegHandle), EXAMPLE_DSPI_MASTER_DMA_BASEADDR, masterTxChannel);

#if (defined(FSL_FEATURE_DSPI_HAS_GASKET) && FSL_FEATURE_DSPI_HAS_GASKET)

DSPI_MasterTransferCreateHandleEDMA(EXAMPLE_DSPI_MASTER_BASEADDR, &g_dspi_edma_m_handle, DSPI_MasterUserCallback,

NULL, &dspiEdmaMasterRxRegToRxDataHandle, NULL,

&dspiEdmaMasterIntermediaryToTxRegHandle);

#else

DSPI_MasterTransferCreateHandleEDMA(EXAMPLE_DSPI_MASTER_BASEADDR, &g_dspi_edma_m_handle, DSPI_MasterUserCallback,

NULL, &dspiEdmaMasterRxRegToRxDataHandle,

&dspiEdmaMasterTxDataToIntermediaryHandle,

&dspiEdmaMasterIntermediaryToTxRegHandle);

#endif

while (1)

{

/* Set up the transfer data */

for (i = 0U; i < TRANSFER_SIZE; i++)

{

masterTxData[i] = (i + loopCount) % 256U;

masterRxData[i] = 0U;

}

/* Print out transmit buffer */

PRINTF("\r\n Master transmit:\r\n");

for (i = 0; i < TRANSFER_SIZE; i++)

{

/* Print 16 numbers in a line */

if ((i & 0x0FU) == 0U)

{

PRINTF("\r\n");

}

PRINTF(" %02X", masterTxData[i]);

}

PRINTF("\r\n");

/* Start master transfer, send data to slave */

isTransferCompleted = false;

masterXfer.txData = masterTxData;

masterXfer.rxData = NULL;

masterXfer.dataSize = TRANSFER_SIZE;

masterXfer.configFlags = kDSPI_MasterCtar0 | EXAMPLE_DSPI_MASTER_PCS_FOR_TRANSFER | kDSPI_MasterPcsContinuous;

if (kStatus_Success !=

DSPI_MasterTransferEDMA(EXAMPLE_DSPI_MASTER_BASEADDR, &g_dspi_edma_m_handle, &masterXfer))

{

PRINTF("There is error when start DSPI_MasterTransferEDMA \r\n ");

}

/* Wait until transfer completed */

while (!isTransferCompleted)

{

}

/* Delay to wait slave is ready */

if (SysTick_Config(SystemCoreClock / 1000U))

{

while (1)

{

}

}

/* Delay 20 ms */

g_systickCounter = 20U;

while (g_systickCounter != 0U)

{

}

/* Start master transfer, receive data from slave */

isTransferCompleted = false;

masterXfer.txData = NULL;

masterXfer.rxData = masterRxData;

masterXfer.dataSize = TRANSFER_SIZE;

masterXfer.configFlags = kDSPI_MasterCtar0 | EXAMPLE_DSPI_MASTER_PCS_FOR_TRANSFER | kDSPI_MasterPcsContinuous;

if (kStatus_Success !=

DSPI_MasterTransferEDMA(EXAMPLE_DSPI_MASTER_BASEADDR, &g_dspi_edma_m_handle, &masterXfer))

{

PRINTF("There is error when start DSPI_MasterTransferEDMA \r\n ");

}

/* Wait until transfer completed */

while (!isTransferCompleted)

{

}

errorCount = 0;

for (i = 0; i < TRANSFER_SIZE; i++)

{

if (masterTxData[i] != masterRxData[i])

{

errorCount++;

}

}

if (errorCount == 0)

{

PRINTF(" \r\nDSPI transfer all data matched! \r\n");

/* Print out receive buffer */

PRINTF("\r\n Master received:\r\n");

for (i = 0; i < TRANSFER_SIZE; i++)

{

/* Print 16 numbers in a line */

if ((i & 0x0FU) == 0U)

{

PRINTF("\r\n");

}

PRINTF(" %02X", masterRxData[i]);

}

PRINTF("\r\n");

}

else

{

PRINTF(" \r\nError occurred in DSPI transfer ! \r\n");

}

/* Wait for press any key */

PRINTF("\r\n Press any key to run again\r\n");

GETCHAR();

/* Increase loop count to change transmit buffer */

loopCount++;

}

}

I think this could help you to port in the k21.

Best regards,

Pavel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

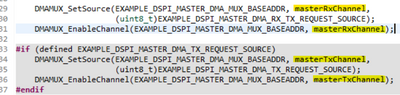

Hi @Pavel_Hernandez , thanks for the answer. I already try to use only one macro (disabling the RX part), but it is not working. The callback is not being called:

(...)

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I suggest reviewing the code because in the original code there are using 2 sources of the DMAMUX but with the SPI2 you need to modify your code to use only one source.

This configuration handler is for an inexistent source.

Best regards,

Pavel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

What do you mean to reviewing the code? Please, could you send the twrk21f120m_dspi_edma_b2b_transfer_master example working for SPI2?

thanks

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

Let me get 2 twr-k21 for making a test.

Best regards,

Pavel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I could not get the twr-k21 but I make some tests with the frdm-k22 this is the code I modified and tested.

/*

* Copyright (c) 2015, Freescale Semiconductor, Inc.

* Copyright 2016-2017 NXP

* All rights reserved.

*

* SPDX-License-Identifier: BSD-3-Clause

*/

#include "fsl_device_registers.h"

#include "fsl_debug_console.h"

#include "fsl_dspi.h"

#include "pin_mux.h"

#include "clock_config.h"

#include "board.h"

#include "fsl_dspi_edma.h"

#include "fsl_edma.h"

#include "fsl_dmamux.h"

/*******************************************************************************

* Definitions

******************************************************************************/

#define EXAMPLE_DSPI_MASTER_BASEADDR SPI1

#define EXAMPLE_DSPI_MASTER_DMA_MUX_BASEADDR DMAMUX

#define EXAMPLE_DSPI_MASTER_DMA_BASEADDR DMA0

#define EXAMPLE_DSPI_MASTER_DMA_TX_RX_REQUEST_SOURCE kDmaRequestMux0SPI1

//#define EXAMPLE_DSPI_MASTER_DMA_TX_REQUEST_SOURCE kDmaRequestMux0SPI0Tx

#define DSPI_MASTER_CLK_SRC DSPI1_CLK_SRC

#define DSPI_MASTER_CLK_FREQ CLOCK_GetFreq(DSPI1_CLK_SRC)

#define EXAMPLE_DSPI_MASTER_PCS_FOR_INIT kDSPI_Pcs0

#define EXAMPLE_DSPI_MASTER_PCS_FOR_TRANSFER kDSPI_MasterPcs0

#define EXAMPLE_DSPI_DEALY_COUNT 0xfffffU

#define TRANSFER_SIZE 64U /* Transfer dataSize */

#define TRANSFER_BAUDRATE 500000U /* Transfer baudrate - 500k */

/*******************************************************************************

* Prototypes

******************************************************************************/

/* DSPI user callback */

void DSPI_MasterUserCallback(SPI_Type *base, dspi_master_edma_handle_t *handle, status_t status, void *userData);

/*******************************************************************************

* Variables

******************************************************************************/

uint8_t masterRxData[TRANSFER_SIZE] = {0};

uint8_t masterTxData[TRANSFER_SIZE] = {0};

dspi_master_edma_handle_t g_dspi_edma_m_handle;

edma_handle_t dspiEdmaMasterRxRegToRxDataHandle;

#if (!(defined(FSL_FEATURE_DSPI_HAS_GASKET) && FSL_FEATURE_DSPI_HAS_GASKET))

edma_handle_t dspiEdmaMasterTxDataToIntermediaryHandle;

#endif

edma_handle_t dspiEdmaMasterIntermediaryToTxRegHandle;

volatile bool isTransferCompleted = false;

volatile uint32_t g_systickCounter = 20U;

/*******************************************************************************

* Code

******************************************************************************/

void SysTick_Handler(void)

{

if (g_systickCounter != 0U)

{

g_systickCounter--;

}

}

void DSPI_MasterUserCallback(SPI_Type *base, dspi_master_edma_handle_t *handle, status_t status, void *userData)

{

if (status == kStatus_Success)

{

PRINTF("This is DSPI master edma transfer completed callback. \r\n\r\n");

}

isTransferCompleted = true;

}

/*!

* @brief Main function

*/

int main(void)

{

BOARD_InitBootPins();

BOARD_InitBootClocks();

BOARD_InitDebugConsole();

PRINTF("DSPI board to board edma example.\r\n");

PRINTF("This example use one board as master and another as slave.\r\n");

PRINTF("Master and slave uses EDMA way. Slave should start first. \r\n");

PRINTF("Please make sure you make the correct line connection. Basically, the connection is: \r\n");

PRINTF("DSPI_master -- DSPI_slave \r\n");

PRINTF(" CLK -- CLK \r\n");

PRINTF(" PCS -- PCS \r\n");

PRINTF(" SOUT -- SIN \r\n");

PRINTF(" SIN -- SOUT \r\n");

PRINTF(" GND -- GND \r\n");

/* DMA Mux setting and EDMA init */

uint32_t masterRxChannel, masterTxChannel;

edma_config_t userConfig;

masterRxChannel = 0U;

masterTxChannel = 1U;

/* If DSPI instances support Gasket feature, only two channels are needed. */

#if (!(defined(FSL_FEATURE_DSPI_HAS_GASKET) && FSL_FEATURE_DSPI_HAS_GASKET))

uint32_t masterIntermediaryChannel;

masterIntermediaryChannel = 2U;

#endif

/* DMA MUX init */

DMAMUX_Init(EXAMPLE_DSPI_MASTER_DMA_MUX_BASEADDR);

DMAMUX_SetSource(EXAMPLE_DSPI_MASTER_DMA_MUX_BASEADDR, masterRxChannel, (uint8_t)EXAMPLE_DSPI_MASTER_DMA_TX_RX_REQUEST_SOURCE);

DMAMUX_EnableChannel(EXAMPLE_DSPI_MASTER_DMA_MUX_BASEADDR, masterRxChannel);

#if (defined EXAMPLE_DSPI_MASTER_DMA_TX_REQUEST_SOURCE)

DMAMUX_SetSource(EXAMPLE_DSPI_MASTER_DMA_MUX_BASEADDR, masterTxChannel, (uint8_t)EXAMPLE_DSPI_MASTER_DMA_TX_REQUEST_SOURCE);

DMAMUX_EnableChannel(EXAMPLE_DSPI_MASTER_DMA_MUX_BASEADDR, masterTxChannel);

#endif

/* EDMA init */

/*

* userConfig.enableRoundRobinArbitration = false;

* userConfig.enableHaltOnError = true;

* userConfig.enableContinuousLinkMode = false;

* userConfig.enableDebugMode = false;

*/

EDMA_GetDefaultConfig(&userConfig);

EDMA_Init(EXAMPLE_DSPI_MASTER_DMA_BASEADDR, &userConfig);

uint32_t srcClock_Hz;

uint32_t errorCount;

uint32_t loopCount = 1U;

uint32_t i;

dspi_master_config_t masterConfig;

dspi_transfer_t masterXfer;

/* Master config */

masterConfig.whichCtar = kDSPI_Ctar0;

masterConfig.ctarConfig.baudRate = TRANSFER_BAUDRATE;

masterConfig.ctarConfig.bitsPerFrame = 8;

masterConfig.ctarConfig.cpol = kDSPI_ClockPolarityActiveHigh;

masterConfig.ctarConfig.cpha = kDSPI_ClockPhaseFirstEdge;

masterConfig.ctarConfig.direction = kDSPI_MsbFirst;

masterConfig.ctarConfig.pcsToSckDelayInNanoSec = 1000000000U / TRANSFER_BAUDRATE;

masterConfig.ctarConfig.lastSckToPcsDelayInNanoSec = 1000000000U / TRANSFER_BAUDRATE;

masterConfig.ctarConfig.betweenTransferDelayInNanoSec = 1000000000U / TRANSFER_BAUDRATE;

masterConfig.whichPcs = EXAMPLE_DSPI_MASTER_PCS_FOR_INIT;

masterConfig.pcsActiveHighOrLow = kDSPI_PcsActiveLow;

masterConfig.enableContinuousSCK = false;

masterConfig.enableRxFifoOverWrite = false;

masterConfig.enableModifiedTimingFormat = false;

masterConfig.samplePoint = kDSPI_SckToSin0Clock;

srcClock_Hz = DSPI_MASTER_CLK_FREQ;

DSPI_MasterInit(EXAMPLE_DSPI_MASTER_BASEADDR, &masterConfig, srcClock_Hz);

/* Set up dspi master */

memset(&(dspiEdmaMasterRxRegToRxDataHandle), 0, sizeof(dspiEdmaMasterRxRegToRxDataHandle));

#if (!(defined(FSL_FEATURE_DSPI_HAS_GASKET) && FSL_FEATURE_DSPI_HAS_GASKET))

memset(&(dspiEdmaMasterTxDataToIntermediaryHandle), 0, sizeof(dspiEdmaMasterTxDataToIntermediaryHandle));

#endif

memset(&(dspiEdmaMasterIntermediaryToTxRegHandle), 0, sizeof(dspiEdmaMasterIntermediaryToTxRegHandle));

EDMA_CreateHandle(&(dspiEdmaMasterRxRegToRxDataHandle), EXAMPLE_DSPI_MASTER_DMA_BASEADDR, masterRxChannel);

#if (!(defined(FSL_FEATURE_DSPI_HAS_GASKET) && FSL_FEATURE_DSPI_HAS_GASKET))

EDMA_CreateHandle(&(dspiEdmaMasterTxDataToIntermediaryHandle), EXAMPLE_DSPI_MASTER_DMA_BASEADDR, masterIntermediaryChannel);

#endif

EDMA_CreateHandle(&(dspiEdmaMasterIntermediaryToTxRegHandle), EXAMPLE_DSPI_MASTER_DMA_BASEADDR, masterTxChannel);

#if (defined(FSL_FEATURE_DSPI_HAS_GASKET) && FSL_FEATURE_DSPI_HAS_GASKET)

DSPI_MasterTransferCreateHandleEDMA(EXAMPLE_DSPI_MASTER_BASEADDR, &g_dspi_edma_m_handle, DSPI_MasterUserCallback,

NULL, &dspiEdmaMasterRxRegToRxDataHandle, NULL,

&dspiEdmaMasterIntermediaryToTxRegHandle);

#else

DSPI_MasterTransferCreateHandleEDMA(EXAMPLE_DSPI_MASTER_BASEADDR, &g_dspi_edma_m_handle, DSPI_MasterUserCallback,

NULL, &dspiEdmaMasterRxRegToRxDataHandle,

&dspiEdmaMasterTxDataToIntermediaryHandle,

&dspiEdmaMasterIntermediaryToTxRegHandle);

#endif

while (1)

{

/* Set up the transfer data */

for (i = 0U; i < TRANSFER_SIZE; i++)

{

masterTxData[i] = (i + loopCount) % 256U;

masterRxData[i] = 0U;

}

/* Print out transmit buffer */

PRINTF("\r\n Master transmit:\r\n");

for (i = 0; i < TRANSFER_SIZE; i++)

{

/* Print 16 numbers in a line */

if ((i & 0x0FU) == 0U)

{

PRINTF("\r\n");

}

PRINTF(" %02X", masterTxData[i]);

}

PRINTF("\r\n");

/* Start master transfer, send data to slave */

isTransferCompleted = false;

masterXfer.txData = masterTxData;

masterXfer.rxData = NULL;

masterXfer.dataSize = TRANSFER_SIZE;

masterXfer.configFlags = kDSPI_MasterCtar0 | EXAMPLE_DSPI_MASTER_PCS_FOR_TRANSFER | kDSPI_MasterPcsContinuous;

if (kStatus_Success !=

DSPI_MasterTransferEDMA(EXAMPLE_DSPI_MASTER_BASEADDR, &g_dspi_edma_m_handle, &masterXfer))

{

PRINTF("There is error when start DSPI_MasterTransferEDMA \r\n ");

}

/* Wait until transfer completed */

while (!isTransferCompleted)

{

}

/* Delay to wait slave is ready */

if (SysTick_Config(SystemCoreClock / 1000U))

{

while (1)

{

}

}

/* Delay 20 ms */

g_systickCounter = 20U;

while (g_systickCounter != 0U)

{

}

/* Start master transfer, receive data from slave */

isTransferCompleted = false;

masterXfer.txData = NULL;

masterXfer.rxData = masterRxData;

masterXfer.dataSize = TRANSFER_SIZE;

masterXfer.configFlags = kDSPI_MasterCtar0 | EXAMPLE_DSPI_MASTER_PCS_FOR_TRANSFER | kDSPI_MasterPcsContinuous;

if (kStatus_Success !=

DSPI_MasterTransferEDMA(EXAMPLE_DSPI_MASTER_BASEADDR, &g_dspi_edma_m_handle, &masterXfer))

{

PRINTF("There is error when start DSPI_MasterTransferEDMA \r\n ");

}

/* Wait until transfer completed */

while (!isTransferCompleted)

{

}

errorCount = 0;

for (i = 0; i < TRANSFER_SIZE; i++)

{

if (masterTxData[i] != masterRxData[i])

{

errorCount++;

}

}

if (errorCount == 0)

{

PRINTF(" \r\nDSPI transfer all data matched! \r\n");

/* Print out receive buffer */

PRINTF("\r\n Master received:\r\n");

for (i = 0; i < TRANSFER_SIZE; i++)

{

/* Print 16 numbers in a line */

if ((i & 0x0FU) == 0U)

{

PRINTF("\r\n");

}

PRINTF(" %02X", masterRxData[i]);

}

PRINTF("\r\n");

}

else

{

PRINTF(" \r\nError occurred in DSPI transfer ! \r\n");

}

/* Wait for press any key */

PRINTF("\r\n Press any key to run again\r\n");

GETCHAR();

/* Increase loop count to change transmit buffer */

loopCount++;

}

}

I think this could help you to port in the k21.

Best regards,

Pavel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

thanks!! It works in MK21 for both SPI1 and SP2.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

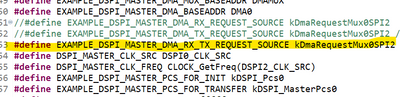

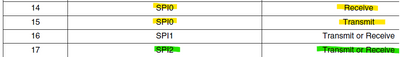

I review the example and I confirm something in the Reference Manual in the section [Table 3-25. DMA request sources - MUX 0] you can see the sources of the example in yellow.

But the SPI2 only have 1 source for transmit or Receive, and you define tow macros but only need one.

#define EXAMPLE_DSPI_MASTER_DMA_RX_TX_REQUEST_SOURCE kDmaRequestMux0SPI2

Try it and if you have more questions please let me know.

Best regards,

Pavel