- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- KL16 I2S Master Mode - Generating Clock Signals

KL16 I2S Master Mode - Generating Clock Signals

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

KL16 I2S Master Mode - Generating Clock Signals

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I am using the MKL16Z256VMP4 as an I2S master. Can it generate the following synchronized clock frequencies?

- SAI_TX_BCLK 3.072 MHz

- SAI_TX_FS 48 kHz

- I2S_MCLK 6.144/12.288/24.756 MHz

I have read through the KL16 Sub-Family Reference Manual Rev 3.2 but am unsure of how SAI_TX_FS is configured.

Thanks in advance!

Lance

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Lance,

Due to the requirement, the bit clock is 3.072MHz with Transmitter frame sync frequency 48KHz.

3.072MHz/48KHz = 64

So, the data frame need contain 2 words, each word contains 32 bits.

I2S0_TCR4 register [FRSZ] = 0b1; [SYWD] = 0b11111;

I2S0_TCR5 register [WNW] = 0b11111; [W0W] = 0b11111;

Wish it helps.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you.

Why does the data frame need to contain 2 words?

Can this frame sync frequency be used as a clock output when no data is being transmitted or received? This application just needs these three synchronized frequencies to be output.

Lance

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Lance,

I am checking with this issue. I will let you know soon.

Thank you for the patience.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Lance,

Sorry for the later reply.

The frame sync clock will based on SAI Transmit Configuration 4 Register (I2Sx_TCR4) [SYWD] bit about active level bit clock number. When, set data frame with 2 words, each word 32 bit, the total frame sync signal bit clock is (32bit active level + 32bit inactive level, total 64bit ).

When customer need just three clock signals output, it need to continue to transmit the data output(whatever the data value). So, there need to use DMA engineer to move data to SAI Transmit Data Register (I2Sx_TDRn) continuously.

We are curious why customer consider this kind of application of SAI module.

We also suggest customer to use PTC3(CLKOUT) pin to output the I2S_MCLK clock(OSCERCLK) ;

using two TPM modules to output SAI_TX_BCLK clock and SAI_TX_FS clock.

Wish it helps.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Ma Hui,

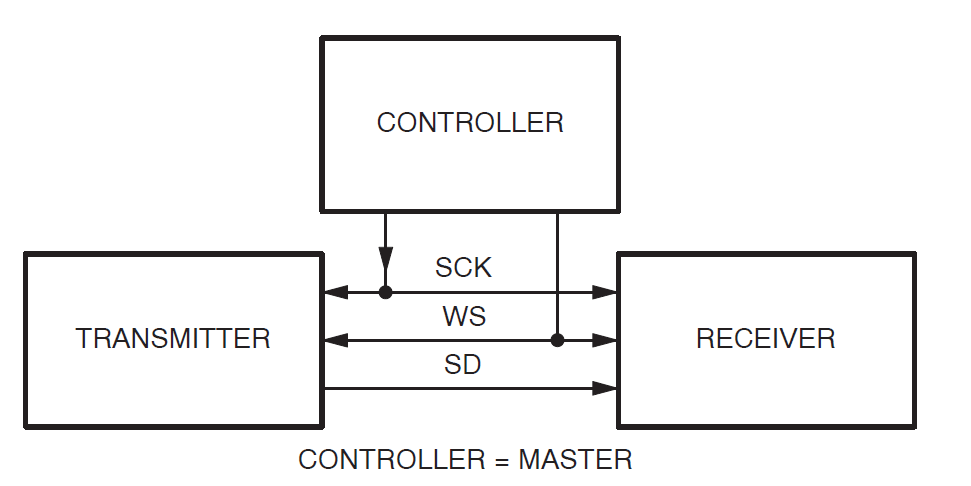

I am trying to use the MCU as the I2S master as shown in the diagram above. Hope it helps.