- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- KEAZN64 SPI CS Goes High inbetween packet

KEAZN64 SPI CS Goes High inbetween packet

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

KEAZN64 SPI CS Goes High inbetween packet

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

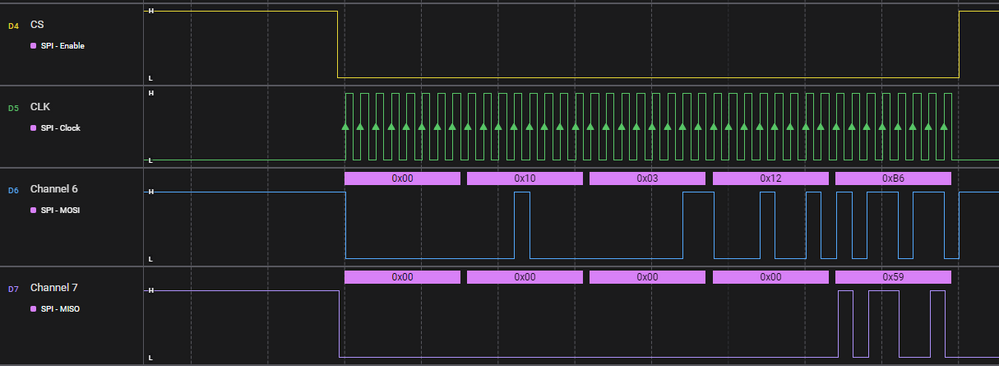

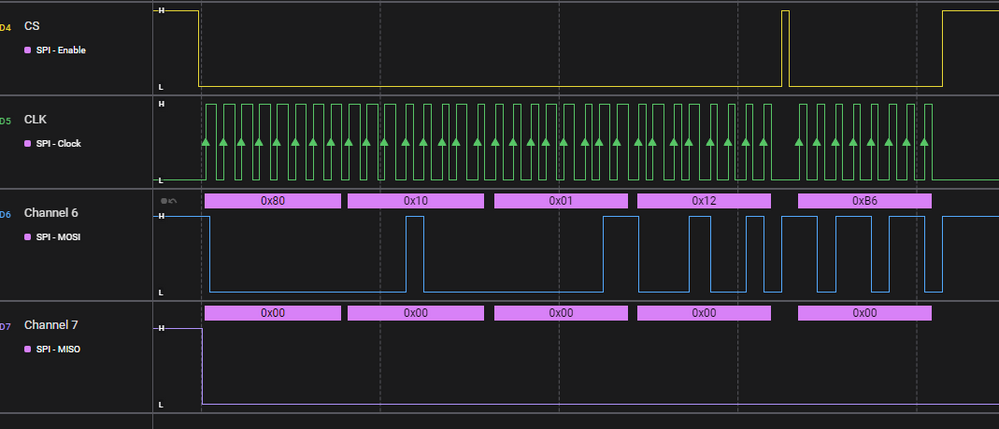

I'm currently interfacing with a device over SPI using the KEAZN64 microcontroller. I'm using Processor Expert in KDS for development, since the later NXP tools do not support the KEA line of micros. The device I'm interfacing with can operate up to 3.6Mhz. I've currently set the clock speed to 500KHz and I can interface over SPI just fine. When I increase the speed to 1MHz I'm seeing a small pulse on the CS line that breaks the existing code. I've attached a picture of a correct packet @500KHz and an incorrect packet @ 1MHz.

500 KHz:

1 MHz:

As you can see in the 1MHz picture, the CS line goes high after the 4th byte for some reason, but this doesn't happen when I run it at 500KHz.

I'm using PE in KDS to generate the SPI code, and here is the diff between 500KHz and 1MHz:

500KHz:

/* SPI0_BR: ??=0,SPPR=0,SPR=4 */

SPI0_BR = (SPI_BR_SPPR(0x00) | SPI_BR_SPR(0x04)); /* Set baud rate register */

1MHz:

/* SPI0_BR: ??=0,SPPR=0,SPR=3 */

SPI0_BR = (SPI_BR_SPPR(0x00) | SPI_BR_SPR(0x03)); /* Set baud rate register */

I'd appreciate any help!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry, we no longer support processor expert, neither KDS, we recommend you to switch to S32 Design Studio for Arm (https://www.nxp.com/design/software/development-software/s32-design-studio-ide/s32-design-studio-for...)