- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- ARM Microcontrollers

- :

- Kinetis微控制器知识库

- :

- K64 FlexTimer Output Compare mode CnV register update Test

K64 FlexTimer Output Compare mode CnV register update Test

K64 FlexTimer Output Compare mode CnV register update Test

K64 FlexTimer Output Compare mode CnV register update Test

Test environment:

FRDM-K64F Rev.D

IAR ARM Workbench IDE V8.30.1

MCUXpresso SDK for FRDM-K64F v2.4.2(2018-08-02)

Test project is [ftm_output_compare] located with default path: ..\FRDM-K64F\boards\frdmk64f\driver_examples\ftm\output_compare

Test reason to verify the CnV register is updated on the next FTM counter change.

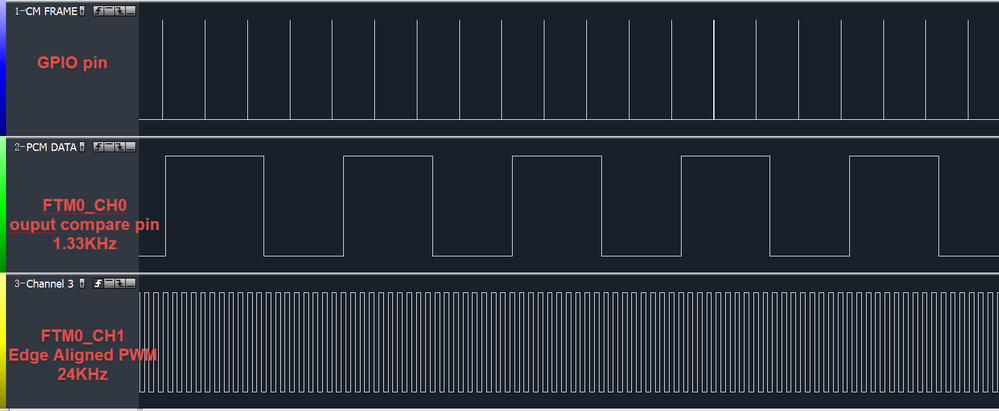

Three test signals:

FTM0_CH0 pin as output compare pin will generate square signal with 1.33KHz .

FTM0_CH1 pin generate 24KHz Edge-Aligned PWM signal(High-true pulses (clear Output on match)) with 50% duty cycle as FTM counter monitor.

When FTM counter change, the FTM0_CH1 will toggle to output high voltage.

Test using a delay() function to emulate modify FTM0_CH0 output compare mode and CnV value periodically.

There is a GPIO pin will toggle after each delay() function to detect/verify the CnV value actual load point.

FlexTimer module setting:

The FTM0 refer clock is 60MHz

For the FTM0_CH1 pin generate 24KHz PWM signal, the FTM0 MOD value is fixed to 0x9C3 (60MHz/24KHz = 2500).

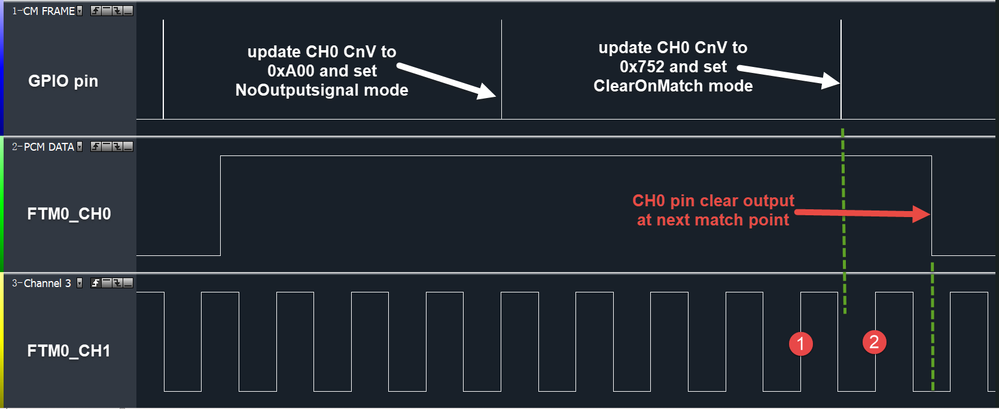

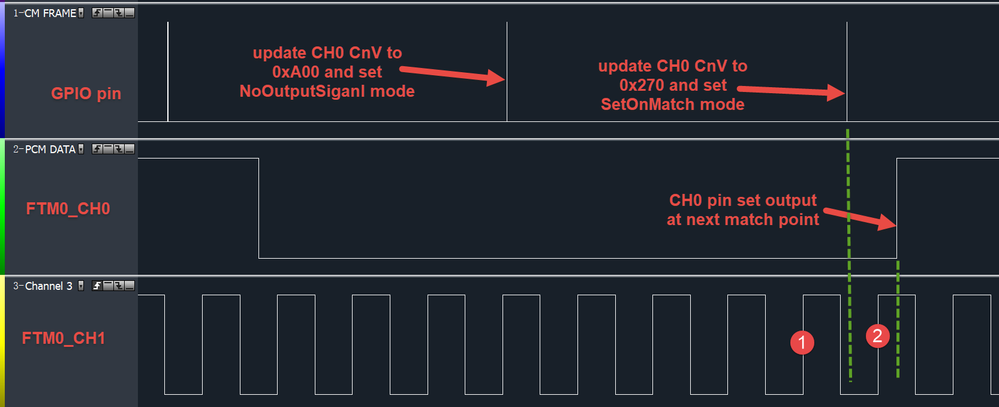

Below is the overall signals:

Test Process Record:

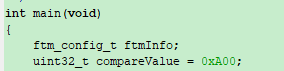

During FTM0 module initialization, set the FTM0_CH0 pin output compare value to 0xA00 (more than MOD register value (0x9C3)) with below code:

Set the CnV value more than MOD register is to avoid the output compare be set during at start.

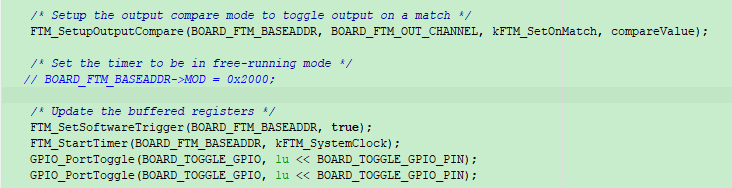

After that, enable FTM0 counter and toggle GPIO pin to set a mark:

After delay, toggle GPIO pin and update CnV register to 0x270 (the match point is half of the PWM high voltage).

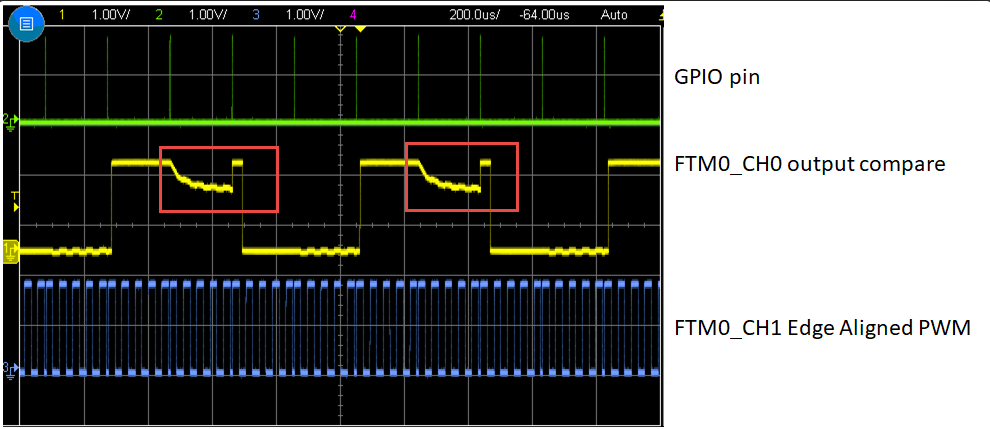

The actual signal is :

After the first CH0 output compare set match, before set CH0 pin clear on match.

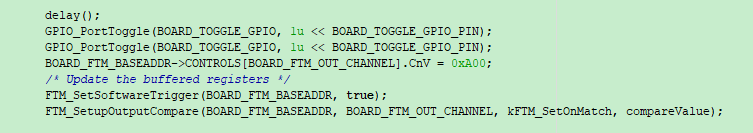

It need to keep the CH0 pin with same output compare mode and set CnV back to 0xA00 (more than MOD) again with below code:

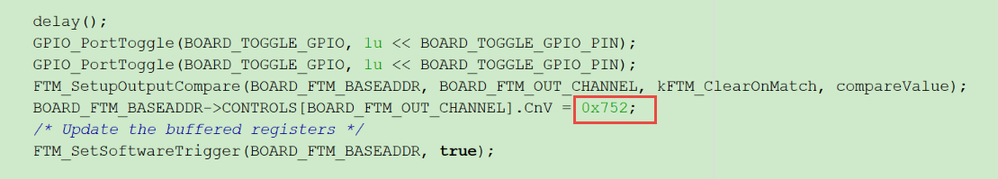

Then we set CH0 with clear on match mode and update CnV value to 0x752 (middle of CH1 PWM low voltage):

The actual signal is:

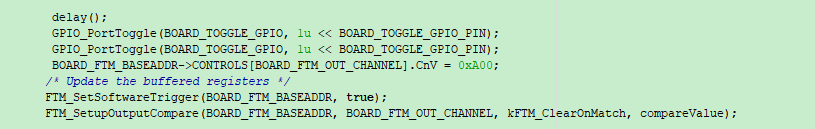

With the similar code, before next CH0 set on match, it need to keep the CH0 pin with same match compare mode setting and CnV change back to 0xA00 (more than MOD).

The actual signal is below:

Note: During the output compare signal compare mode set/clear change phase, it need to keep previous output compare mode setting, please don't using kFTM_NoOutputSignal setting at code. Otherwise, the output compare signal will exist decay:

Test Result:

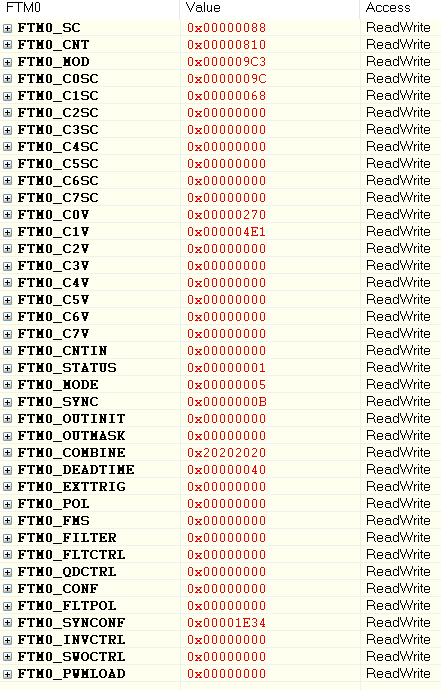

From FTM0 register value, the FTM0_SYNCONF[SWRSTCNT] bit is clear, which means select Legacy PWM synchronization method.

The legacy PWM synchronization method will update Output Compare mode CnV register value at the next FTM counter change.

The actual signal also verify it.

Below is FTM0 all registers value:

For the more detailed info, please check the original thread at here.

Please check attachment about test code.

What to change in the code so that I can use the RGB LED on board to get the result. such that the led is on when the PWM is high and led is off when the PWM is low

Hi

None of the RGB LEDs on the FRDM-K64F are connected to pins that support this output so you would need to rewire them to do it.

Alternatively, the timer's can be used to generate DMA transfers to the ports in question to emulate it, but that is not as efficient and so is only use in emergencies.

Regards

Mark