- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- How to modify FTFL_FOPT register on Kinetis K10 to change boot options?

How to modify FTFL_FOPT register on Kinetis K10 to change boot options?

Hello.

I want to activate the low-power boot modus. Therefore I need to set the LPBOOT bit in the FTFL_FOPT register to zero. The register value is stored in flash. But in the reference manual there is no description how to chance the value.

Can somebody explain how to change the value?

MCU: MK10DX256VLH7

已解决! 转到解答。

Hello Peter:

The procedure to write to specific Flash address is compiler specific, hence different between IDEs. That is why it is not mentioned in the Reference Manual.

- If using CodeWarrior, you can declare an array in any of your source files (usually one of the startup files) containing the Flash Configuration Field values.

:smileyalert: The .cfmconfig section is declared at address 0x00000400 in the linker file, so you have to include ALL the flash configuration bytes, even with the default values:

/* Flash configuration field */

__attribute__ ((section (".cfmconfig"))) const uint8_t _cfm[0x10] = {

/* NV_BACKKEY3: KEY=0xFF */

0xFFU,

/* NV_BACKKEY2: KEY=0xFF */

0xFFU,

/* NV_BACKKEY1: KEY=0xFF */

0xFFU,

/* NV_BACKKEY0: KEY=0xFF */

0xFFU,

/* NV_BACKKEY7: KEY=0xFF */

0xFFU,

/* NV_BACKKEY6: KEY=0xFF */

0xFFU,

/* NV_BACKKEY5: KEY=0xFF */

0xFFU,

/* NV_BACKKEY4: KEY=0xFF */

0xFFU,

/* NV_FPROT3: PROT=0xFF */

0xFFU,

/* NV_FPROT2: PROT=0xFF */

0xFFU,

/* NV_FPROT1: PROT=0xFF */

0xFFU,

/* NV_FPROT0: PROT=0xFF */

0xFFU,

/* NV_FSEC: KEYEN=1,MEEN=3,FSLACC=3,SEC=2 */

0x7EU,

/* NV_FOPT: ??=1,??=1,??=1,??=1,??=1,NMI_DIS=1,EZPORT_DIS=1,LPBOOT=0 */

0xFEU,

/* NV_FEPROT: EPROT=0xFF */

0xFFU,

/* NV_FDPROT: DPROT=0xFF */

0xFFU

};

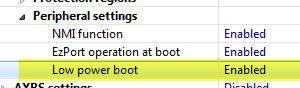

- With Processor Expert this is easier, just enable Low Power Boot from the CPU component settings:

Regards!,

Jorge Gonzalez

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hello Peter:

The procedure to write to specific Flash address is compiler specific, hence different between IDEs. That is why it is not mentioned in the Reference Manual.

- If using CodeWarrior, you can declare an array in any of your source files (usually one of the startup files) containing the Flash Configuration Field values.

:smileyalert: The .cfmconfig section is declared at address 0x00000400 in the linker file, so you have to include ALL the flash configuration bytes, even with the default values:

/* Flash configuration field */

__attribute__ ((section (".cfmconfig"))) const uint8_t _cfm[0x10] = {

/* NV_BACKKEY3: KEY=0xFF */

0xFFU,

/* NV_BACKKEY2: KEY=0xFF */

0xFFU,

/* NV_BACKKEY1: KEY=0xFF */

0xFFU,

/* NV_BACKKEY0: KEY=0xFF */

0xFFU,

/* NV_BACKKEY7: KEY=0xFF */

0xFFU,

/* NV_BACKKEY6: KEY=0xFF */

0xFFU,

/* NV_BACKKEY5: KEY=0xFF */

0xFFU,

/* NV_BACKKEY4: KEY=0xFF */

0xFFU,

/* NV_FPROT3: PROT=0xFF */

0xFFU,

/* NV_FPROT2: PROT=0xFF */

0xFFU,

/* NV_FPROT1: PROT=0xFF */

0xFFU,

/* NV_FPROT0: PROT=0xFF */

0xFFU,

/* NV_FSEC: KEYEN=1,MEEN=3,FSLACC=3,SEC=2 */

0x7EU,

/* NV_FOPT: ??=1,??=1,??=1,??=1,??=1,NMI_DIS=1,EZPORT_DIS=1,LPBOOT=0 */

0xFEU,

/* NV_FEPROT: EPROT=0xFF */

0xFFU,

/* NV_FDPROT: DPROT=0xFF */

0xFFU

};

- With Processor Expert this is easier, just enable Low Power Boot from the CPU component settings:

Regards!,

Jorge Gonzalez

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hello Jorge,

thanks for your answer. I'm using CodeWarrior without Processor Expert. I added the code to my startup-code. It seems to be working. But it seems to me that all clocks are devided by 8 now. Furthermore I'm not able to flash my CPU with the debugger (Segger J-Link) any longer and it's not possible to erase the whole device. The debugger is not able to reset the device. What can I do now?

Edit:

I reduced the JTAG speed from 4 MHz to 1 MHz and I was able to flash the device.

OK, I fixed the problem with the low CPU and peripheral speed. After activating the LP boot mode you have to set the correct clock dividers in the SIM_CLKDIV1 register, since the LP boot has different default values for this register (in comparison to the normal boot mode).