- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Flexbus performance issue

Flexbus performance issue

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Flexbus performance issue

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi! I am working Flexbus connection between mk22 micro and FPGA and trying to achieve maximum throughput in both directions. The configuration is 32 bit address and 32 bit data multiplexed, no wait states, auto-acknowledge.

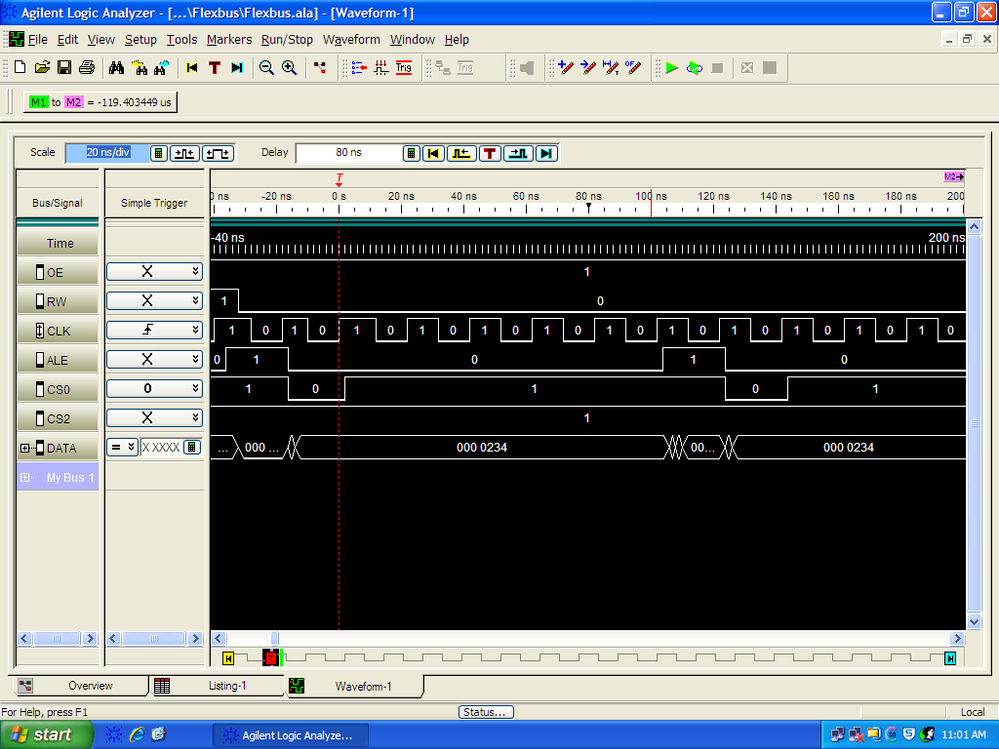

First I have configured it to run at 40 MHz with core clocked at 120MHz. By looking on signals with logic analyzer I have recognized that instead of theoretical 4 cycles for read or write I am achieving only 5 cycles for read and 6 cycles for write.

When I clocked down the processor to 100 MHz and Flexbus speed to 50 MHz it runs 6 cycles for read and 7 cycles for write.

I have also confirmed that control register values are what I expect them to be.

Any consideration why this would be happening?

Addition: while running at 40MHz/120MHz if I add 1 wait state it runs at 5 cycles read or write (as expected).

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Could you provide the Flexbus register configuration and logic analyzer signal scope pictures?

The Flexbus clock could up to 50MHz.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi!

The register configuration is following:

FB_CSAR0 = (uint32)&MRAM_START_ADDRESS;

FB_CSCR0 = 0;

FB_CSCR0 |= FB_CSCR_ASET(0x0); // assert chip select on second clock edge after address is asserted

FB_CSCR0 |= FB_CSCR_RDAH(0x0); // Read Address Hold or Deselect

FB_CSCR0 |= FB_CSCR_WRAH(0x0); // Write Address Hold or Deselect

FB_CSCR0 |= FB_CSCR_WS(0x0); // 0 wait state - may need a wait state depending on the bus speed

FB_CSCR0 |= FB_CSCR_AA_MASK; // auto-acknowledge

FB_CSCR0 |= FB_CSCR_PS(0); // 32-bit port

FB_CSMR0 |= FB_CSMR_BAM(0x7); //Set base address mask for 512K address space

//Enable cs signal

FB_CSMR0 |= FB_CSMR_V_MASK;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Sorry for the later reply.

If you could provide the test code?

From the logic analyzer signal, after the Flexbus doing the 32-bit write, then it waiting for the instruction(code execution) to start the next 32-bit data write.

Customer could try with the burst transfer mode, there could do 16 byte burst transfer to enhance Flexbus performance.

Wish it helps.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The test code could not be simpler:

for(n=0x0000;n<0x00400;n+=4) //address offset

{

*(vuint32*)(&MRAM_START_ADDRESS + n) = 0x1234; //write

}

With DMA it managed to write first value in 4 cycles and following in 6, which is obviously better, but still not 4 cycles constantly.

What is your estimation for burst 16 bit writes? 5 cycles?

Thanks, Viktor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

The burst 16 bytes (one line) data read just need using 7 cycles and write need using 8 cycles for 32-bit port.

Wish it helps.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi!

Sounds cool, could you please send me register set-up and some test code for this please?

Thanks, Viktor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Please refer attached code about Flexbus burst transfer, which is using DMA to transfer 16 bytes data from/to Flexbus.

The DMA setting of SOFF and DOFF must be aligned to 16-byte address, otherwise the transfer is not started.

Please check below code about SOFF and DOFF setting:

void K70_DMA_init(void)

{

SIM_SCGC6 |= SIM_SCGC6_DMAMUX0_MASK;

SIM_SCGC7 |= SIM_SCGC7_DMA_MASK;

/*Enable DMA MUX ch 0*/

//DMAMUX0_CHCFG0 |= DMAMUX_CHCFG_ENBL_MASK;// | DMAMUX_CHCFG_SOURCE(63);

DMAMUX0_CHCFG0 = DMAMUX_CHCFG_SOURCE(63);

/*Start the sequence*/

DMA_ERQ |= DMA_ERQ_ERQ0_MASK;

/*** Initialize CH0, MRAM -> FlexBus, transfer 16 bytes ***/

/* Set the Source Address*/

DMA_TCD0_SADDR = (uint32_t)(&RAM_START_ADDRESS);

/* Destination address */

DMA_TCD0_DADDR = (uint32_t)(&MRAM_START_ADDRESS);

/* Source offset*/

DMA_TCD0_SOFF = 0x16; // 1 byte

/*Modulo off and port sizes*/

DMA_TCD0_ATTR = DMA_ATTR_SSIZE(4) | DMA_ATTR_SMOD(0) | DMA_ATTR_DSIZE(4) | DMA_ATTR_DMOD(0); //source 8 bits, Destination size is 16-byte burst //DMA_TCD0_ATTR = DMA_ATTR_SSIZE(2) | DMA_ATTR_DSIZE(2); //source and destination size 2 = 32 bits

/* Transfer size */

DMA_TCD0_NBYTES_MLNO = 16; //16 bytes

/* No adjustment to source address */

DMA_TCD0_SLAST = -32;//-32

/* Destination offset*/

DMA_TCD0_DOFF = 0x16; //16 bytes

/* No link channel, transactions */

DMA_TCD0_CITER_ELINKNO = 2; //2

/* Adjustment to destination address */

DMA_TCD0_DLASTSGA = -32;//-32

/* No link channel, transactions */

DMA_TCD0_BITER_ELINKNO = 2; //2

DMA_TCD0_CSR = DMA_CSR_DREQ_MASK;

//DMA_TCD0_CSR = 0;

}

Wish it helps.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------