- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- Clock deviation

Clock deviation

Clock deviation

Hi NXP community,

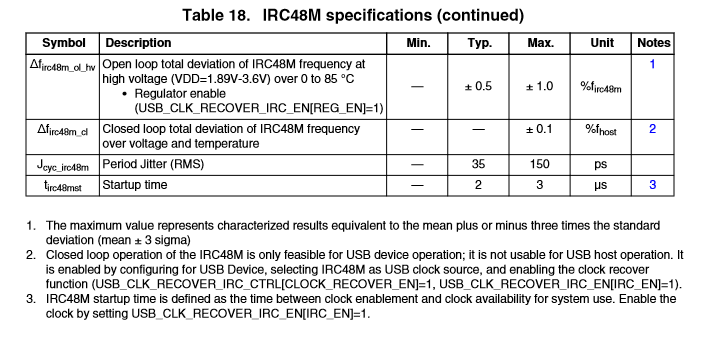

I had a few questions regarding the clock deviation using the 48MIRC on the K24.

Firstly, I understand the from the datasheet that the open loop deviation from 0 to 85 degress is 1%.

Q1. Is it correct to assume that the clock will deviate around 1% (approx. +/- 480000 clocks) between 0 to 85 degrees? Is there some kind of temperature distribution chart for the deviation?

Q2. How will this clock deviation trickle down to the other clocks, bus clock and flash clock? We want to calculate effect of clock deviation of each peripheral i.e., SPI, I2C, ADC and UART and in turn compare it with the tolerance given in the datasheet for these peripherals.

Any input will be very much appreciated.

Thank you

Sachin

Hi Sachin,

1. yes, clock will deviate around 1% (approx. +/- 480000 clocks) between 0 to 85 degrees. But there is no such a chart.

2. If you use IRC48 as system clock source, of course it will trickle down to whole system. The deviation is proportional.

Regards,

Jing