- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- MCUXpresso软件和工具

- :

- Kinetis Design Studio

- :

- frdm-K64F clock setting

frdm-K64F clock setting

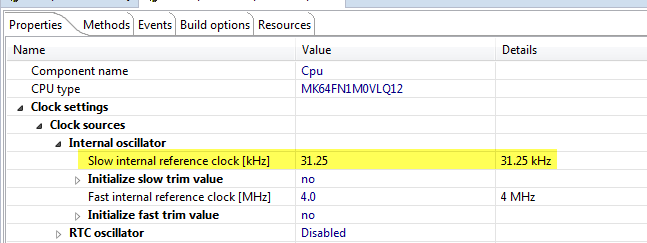

Hi, I have the clock on my frdm-K64F set to 120mhz thanks to Erich Styger's article. But in my PPG component (KDS 3.0) the timing period steps are all decimal equivalents of one third. Like .33333 or .6666 microseconds. Is it possible to set the clock to another value so that the PPG times and steps will be even multiples of a microsecond? Like .5 or 1.0 usec? How would I set that up?

已解决! 转到解答。

Hi,

the solution is to trim the Internal oscillator to 31.25KHz.

thus we can get a integer number MCG FLL output. so setting PPG period as 1us is also possible.

see my attached demo code.

can this help you?

Have a great day,

Zhang Jun

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi,

the solution is to trim the Internal oscillator to 31.25KHz.

thus we can get a integer number MCG FLL output. so setting PPG period as 1us is also possible.

see my attached demo code.

can this help you?

Have a great day,

Zhang Jun

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------