- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- 製品フォーラム

- :

- デジタルシグナルコントローラ

- :

- Re: PCA9698DGG is not working

PCA9698DGG is not working

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

PCA9698DGG is not working

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi ALL

I am evaluating PCA9698DGG, but PCA9698DGG is not working.

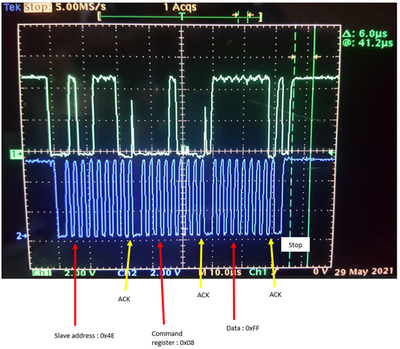

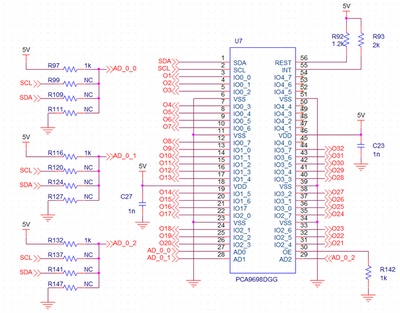

You can see the waveform and schematic as like below.

The waveform capture conditions are below.

- SCL frequency : 400KHz

- Slave address 0x4E

- Command register : 0x08

- Data : 0xFF

- OE pin : GND

- MCU : ATMEGA128

Some strange thing is that SDA signal is very fast drop down after received ACK.

Also, I had changed SCL frequency and Slave address, but result is same.

Could you please help this issue?

Best regards.

JH Kim

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

Regarding to datasheet, output enable when OEPOL = 1.

But in my case, output enable when OEPOL = 0

Is PCA9698DGG datasheet correct on OEPOL and OE Pin?

Thanks

JH Kim

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

OEPOL bit controls the polarity of OE pin.

– OEPOL = 0: OE pin is active LOW.

– OEPOL = 1: OE pin is active HIGH (equivalent to OE pin).

when OEPOL set to 0,low OE active.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

The pull up resistors are located at MCU side. The value is 1.5Kohm.

I think normal working I2C, but PCA9689 output is "0" level under below condition.

- SCL frequency : 400KHz

- Slave address 0x4E

- Command register : 0x08

- Data : 0xFF

- OE pin : GND

- MCU : ATMEGA128

I think PCA9689 output is high level under upper condition.

I don't know what's wrong with no output.

Could you please adivce?

Thanks,

JH Kim

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

1: What's the result when your drop down the frequency?

2:what's the pull up resistors of SDA/SCL of PCA8698?